# INTERPOSER PLATFORMS FEATURING POLYMER-ENHANCED THROUGH SILICON VIAS FOR MICROELECTRONIC SYSTEMS

A Dissertation Presented to The Academic Faculty

by

Paragkumar A. Thadesar

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology May 2015

Copyright © 2015 by Paragkumar A. Thadesar

# INTERPOSER PLATFORMS FEATURING POLYMER-ENHANCED THROUGH SILICON VIAS FOR MICROELECTRONIC SYSTEMS

## Approved by:

Dr. Muhannad Bakir, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Oliver Brand School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. John Cressler School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Hua Wang School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Suresh Sitaraman The George W. Woodruff School of Mechanical Engineering Georgia Institute of Technology

Date Approved: April 1, 2015

Dedicated to my parents Ajaybhai and Pallaviben,

wife Neha, brother Chirag, and sister Krishna

for their endless support.

# **ACKNOWLEDGEMENTS**

I gratefully acknowledge the support from Dr. Muhannad Bakir in every phase of my research, making each phase exciting, challenging and worth pursuing.

I am thankful to Ashish Dembla, Hanju Oh, Chaoqi Zhang, Muneeb Zia, William Wahby, James Yang, Thomas Sarvey, Li Zheng and Yue Zhang for constructive feedback on my research and helping create a great environment for exchange of exciting ideas. I wish to thank Xi Liu and Dr. Suresh Sitaraman for an exciting collaboration. I am thankful to Song Hu and Dr. Hua Wang for help with time-domain measurements. I am thankful to Cagri Ulusoy, Peter Song, Wasif Khan and Dr. John Cressler for help with antenna and D-band measurements.

I wish to thank the cleanroom staff, in particular Gary Spinner, Tran-Vinh Nguyen, Charlie Suh and Hang Chen, at the Georgia Tech's Institute for Electronics and Nan-otechnology (IEN) for keeping the tools functional, and help during weekdays and even holidays.

I am greatly thankful to IBM for selecting me for the IBM Ph.D. Fellowship for the 2014-2015 academic year. I am greatly thankful to Dr. Subramanian Iyer and Dr. Xiaoxiong Gu from IBM and Ramakanth Alapati from GLOBALFOUNDRIES for exciting discussions related to my research and their fruitful feedback.

Lastly, I am thankful to my family and friends for their endless support.

# TABLE OF CONTENTS

| DE  | DIC | ATION   | <b>V</b>                                                         | iii |

|-----|-----|---------|------------------------------------------------------------------|-----|

| AC  | KNO | OWLE    | DGEMENTS                                                         | iv  |

| LIS | T O | F TAE   | BLES                                                             | ix  |

| LIS | T O | F FIG   | URES                                                             | X   |

| SU  | MM  | ARY .   |                                                                  | xvi |

| Ι   | INT | RODU    | JCTION                                                           | 1   |

|     | 1.1 | Motiva  | ation                                                            | 1   |

|     |     | 1.1.1   | Demand for High Off-chip Bandwidth                               | 2   |

|     |     | 1.1.2   | Demand for Heterogeneous Integration Platforms                   | 3   |

|     |     | 1.1.3   | Interposers for Heterogeneous Integration                        | 7   |

|     | 1.2 | Resear  | ch Objective and Contribution                                    | 13  |

|     | 1.3 | Organ   | ization                                                          | 16  |

| II  |     |         | R-CLAD AND OPTICAL TSVS: FABRICATION AND TERIZATION              | 17  |

|     | 2.1 | Literat | ture Survey and Analysis                                         | 17  |

|     |     | 2.1.1   | Electrical TSV Fabrication Processes                             | 17  |

|     |     | 2.1.2   | Polymer Liner for TSVs                                           | 18  |

|     |     | 2.1.3   | Optical TSVs                                                     | 22  |

|     | 2.2 | Fabric  | ation of TSVs with Vapor Deposited Parylene Liner                | 23  |

|     | 2.3 | Fabric  | ation of TSVs with Thick Photodefined Polymer Liner              | 26  |

|     | 2.4 | Optica  | ıl TSVs                                                          | 29  |

|     | 2.5 | Mesh-l  | less High Aspect Ratio Via Filling Process for Polymer-clad TSVs | 30  |

|     | 2.6 | Resista | ance and Optical Loss Measurements                               | 33  |

|     | 2.7 | TSV S   | Strain Measurements Using Synchrotron XRD                        | 35  |

|     |     |         | oriani measurements Using Synchrotron Arth                       |     |

|     | 2.9 | Techn  | ology Comparison and Chapter Conclusion                                             | 48       |

|-----|-----|--------|-------------------------------------------------------------------------------------|----------|

| III |     |        | R-EMBEDDED VIAS: TECHNOLOGY DEVELOPMENT CHARACTERIZATION                            | NT<br>50 |

|     | 3.1 | Techn  | ology Description                                                                   | 50       |

|     | 3.2 | Via-to | o-via Capacitance Analysis                                                          | 53       |

|     | 3.3 | Fabric | eation of Polymer-embedded Vias                                                     | 54       |

|     | 3.4 | Crack  | Reduction and Optimum Exposure Dose Determination                                   | 57       |

|     | 3.5 | Fabric | eation Results                                                                      | 61       |

|     | 3.6 | DC M   | leasurements of Polymer-embedded Vias                                               | 63       |

|     | 3.7 | Chapt  | er Conclusion                                                                       | 65       |

| IV  |     |        | R-EMBEDDED VIAS: RF AND TIME-DOMAIN CHAI<br>ZATIONS                                 | R-<br>66 |

|     | 4.1 | Analy  | sis                                                                                 | 66       |

|     |     | 4.1.1  | TSV Frequency-domain Analysis                                                       | 66       |

|     |     | 4.1.2  | TSV Time-domain Analysis                                                            | 71       |

|     | 4.2 | TSV I  | RF De-embedding and Parasitics Extraction                                           | 73       |

|     |     | 4.2.1  | TSV RF Characterization in the Literature and RF Measurement Setup in this Research | 73       |

|     |     | 4.2.2  | Fabrication and RF Measurements of TSVs with Silicon Dioxide Liner                  | 75       |

|     |     | 4.2.3  | De-embedding and ${\cal CG}$ Extraction of Polymer-embedded Vias                    | 77       |

|     | 4.3 | TSV    | Γime-domain Characterization                                                        | 84       |

|     |     | 4.3.1  | TSV Time-domain Measurement Setup and Loopback Measurements                         | 84       |

|     |     | 4.3.2  | Time-domain Measurements of the TSVs with Silicon Dioxide Liner                     | 85       |

|     |     | 4.3.3  | Polymer-embedded Via Time-domain Measurements                                       | 86       |

|     | 4.4 | TSV I  | D-band Characterization                                                             | 90       |

|     |     | 4.4.1  | D-band Measurement Setup                                                            | 90       |

|     |     | 4.4.2  | Fabrication and D-band Measurements of Polymer-embedded Vias                        | 91       |

|    | 4.5 | Techno | ology Comparison and Chapter Conclusion                                                                                | 93  |

|----|-----|--------|------------------------------------------------------------------------------------------------------------------------|-----|

| V  | PLA | ATFOR  | ENTS FOR MIXED-SIGNAL SILICON INTERPOSER<br>RM: APPLICATIONS OF THE PHOTODEFINED POLICED SILICON INTERPOSER TECHNOLOGY |     |

|    | 5.1 | Mixed- | signal Silicon Interposer Platform                                                                                     | 95  |

|    | 5.2 | Polymo | er-enhanced Coaxial TSVs                                                                                               | 96  |

|    |     | 5.2.1  | Fabrication of Coaxial TSVs                                                                                            | 96  |

|    |     | 5.2.2  | One-port Measurements and Impedance Extraction                                                                         | 96  |

|    |     | 5.2.3  | Coupling Measurements                                                                                                  | 100 |

|    |     | 5.2.4  | Coaxial TSVs: Technology Comparison                                                                                    | 102 |

|    | 5.3 | Polymo | er-enhanced W-band Antennas                                                                                            | 104 |

|    |     | 5.3.1  | Antenna Fabrication                                                                                                    | 104 |

|    |     | 5.3.2  | Antenna Measurement                                                                                                    | 105 |

|    |     | 5.3.3  | Antennas: Technology Comparison                                                                                        | 106 |

|    | 5.4 | Polymo | er-enhanced Inductors                                                                                                  | 109 |

|    |     | 5.4.1  | Fabrication of Inductors                                                                                               | 109 |

|    |     | 5.4.2  | One-port Measurements and $Q$ and $L$ Extraction                                                                       | 111 |

|    |     | 5.4.3  | Inductors: Technology Comparison                                                                                       | 114 |

|    | 5.5 | Chapte | er Conclusion                                                                                                          | 114 |

| VI | SUN | MMAR   | Y AND FUTURE WORK                                                                                                      | 116 |

|    | 6.1 | Summa  | ary                                                                                                                    | 116 |

|    |     | 6.1.1  | Polymer-enhanced TSVs                                                                                                  | 117 |

|    |     | 6.1.2  | Polymer-enhanced Inductors and Antennas                                                                                | 117 |

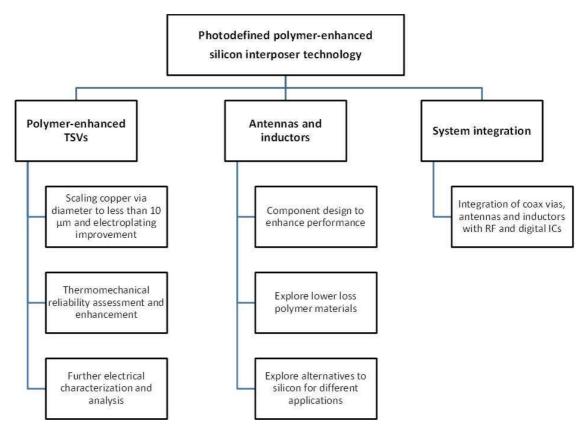

|    | 6.2 | Future | Work                                                                                                                   | 118 |

|    |     | 6.2.1  | Scaling Polymer-enhanced Via Diameter and Electroplating Improvements                                                  | 119 |

|    |     | 6.2.2  | Further Electrical Characterization and Analysis of TSVs                                                               | 119 |

|    |     | 6.2.3  | Polymer-enhanced Antennas and Inductors                                                                                | 120 |

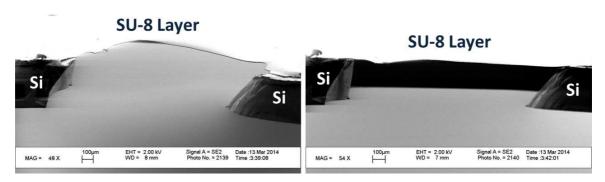

|    |     | 6.2.4  | Exploration of Suspended SU-8 Substrates                                                                               | 120 |

|        | 6.2.5  | Thermomechanical Reliability Assessment and Enhancement | 121 |

|--------|--------|---------------------------------------------------------|-----|

|        | 6.2.6  | System Integration                                      | 121 |

| 6.3    | Resear | rch Conclusion                                          | 122 |

| REFER  | ENCE   | ES                                                      | 123 |

| VITA . |        |                                                         | 137 |

# LIST OF TABLES

| 1  | Comparison of TSV polymer cladding fabrication processes                                          | 20  |

|----|---------------------------------------------------------------------------------------------------|-----|

| 2  | Comparison of TSV stress measurement techniques in the literature                                 | 35  |

| 3  | Comparison of polymer-clad TSVs to other TSV technologies from the literature                     | 49  |

| 4  | Comparison of via fabrication processes in dielectric wells                                       | 52  |

| 5  | Set of experiments for crack reduction and optimum dose determination.                            | 60  |

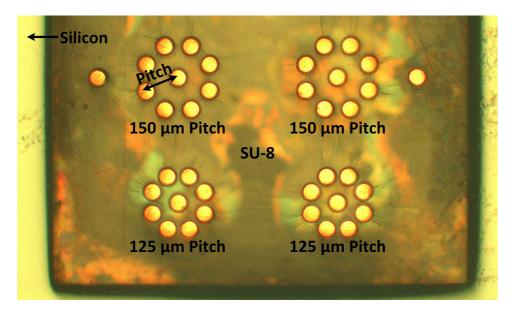

| 6  | Fabricated polymer-embedded via dimensions                                                        | 62  |

| 7  | Comparison of TSV de-embedding techniques in the literature                                       | 77  |

| 8  | Comparison of polymer-embedded vias with other TSV technologies from the literature               | 94  |

| 9  | Comparison of the demonstrated coaxial vias to other coaxial TSV technologies from the literature | 103 |

| 10 | Comparison of the demonstrated antenna to other off-chip antennas from the literature             | 108 |

| 11 | Comparison of the demonstrated inductor to other off-chip inductors from the literature.          | 115 |

# LIST OF FIGURES

| 1  | Consistent increase in transistor count, consistent transistor scaling, and improvements in microprocessor performance (normalized to that of a 386) and gate speeds (approximation of the FO4) since the introduction of CMOS microprocessors [4]                                                                                                      | 2  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Plot showing performance improvement in a many-core chip with high memory bandwidth [9]                                                                                                                                                                                                                                                                 | 3  |

| 3  | Increase in off-chip bandwidth and demand for innovative interconnection and packaging technologies. Images in the plot are from L. Polka et al. [8]                                                                                                                                                                                                    | 4  |

| 4  | Inductor physical models: (a) Lumped model and (b) Equivalent circuit model using the lumped model [15]                                                                                                                                                                                                                                                 | 5  |

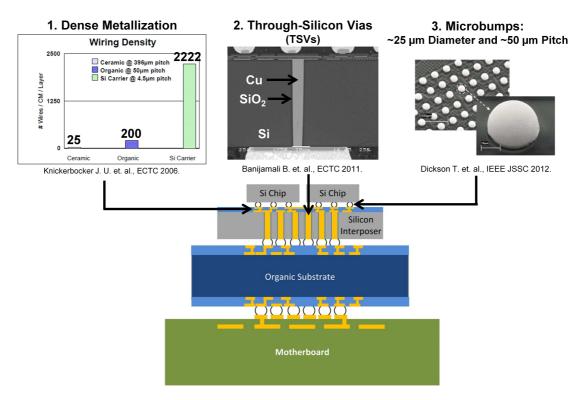

| 5  | Schematic of a 2.5D system using silicon interposer technology with key components shown [24,25,29]                                                                                                                                                                                                                                                     | 8  |

| 6  | 2.5D system demonstrations in the literature [26–30]                                                                                                                                                                                                                                                                                                    | 9  |

| 7  | (a) Bow simulation for thinned interposer dice and wafer after TSV, BEOL and bump fabrication, [28] and (b) warpage measurement of silicon interposers from the BGA pad side after chip mount and underfill [35]                                                                                                                                        | 11 |

| 8  | Impact of TSV length on insertion loss and eye diagram [36]                                                                                                                                                                                                                                                                                             | 12 |

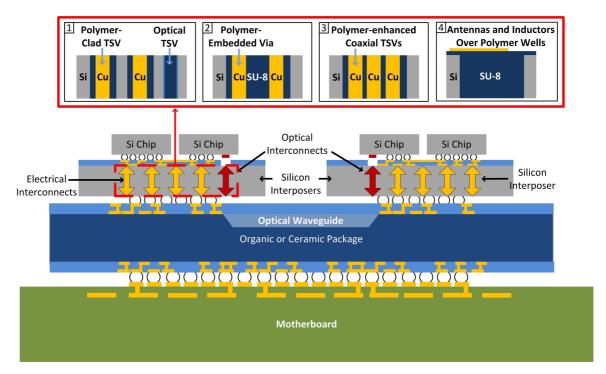

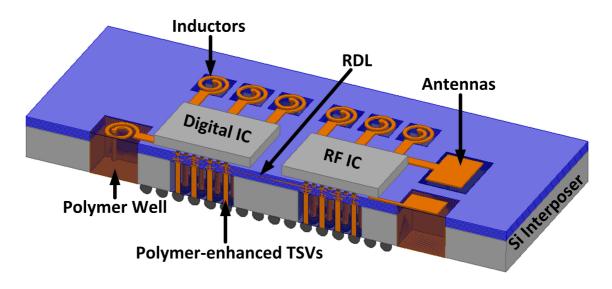

| 9  | Envisioned silicon interposer based system featuring photodefined (a) polymer-clad TSVs and optical TSVs that can be fabricated simultaneously, (b) polymer-embedded vias, (c) polymer-enhanced coaxial vias, and (d) polymer-enhanced inductors and antennas                                                                                           | 13 |

| 10 | Comparison between conventional and photodefined TSVs for silicon interposers                                                                                                                                                                                                                                                                           | 15 |

| 11 | TSV fabrication processes                                                                                                                                                                                                                                                                                                                               | 18 |

| 12 | Comparison of TSV dielectric capacitance                                                                                                                                                                                                                                                                                                                | 21 |

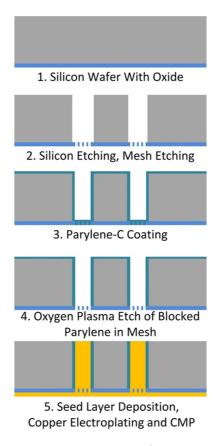

| 13 | Fabrication process of parylene-clad TSVs                                                                                                                                                                                                                                                                                                               | 24 |

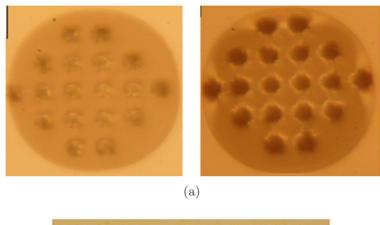

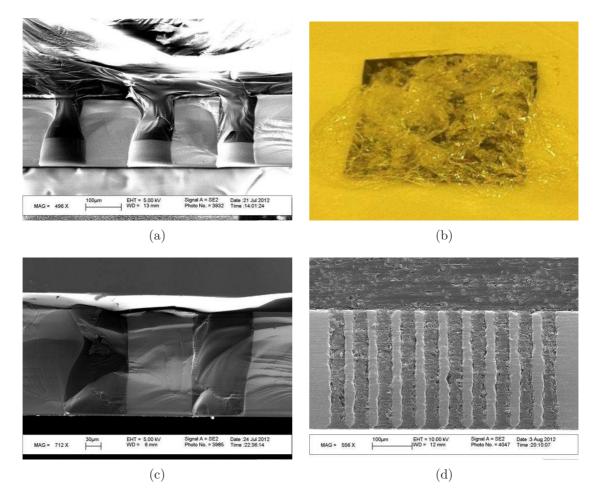

| 14 | Parylene-clad TSV processing results (a) after mesh fabrication and Parylene-C deposition (left) and after oxygen plasma etch of Parylene blocking (right), and (b) after CMP showing the top view of the fabricated 390 $\mu$ m tall Parylene-clad TSVs with $\sim$ 48 $\mu$ m diameter copper vias surrounded by a $\sim$ 2.25 $\mu$ m thick cladding | 25 |

| 15 | Fabrication process for photodefined polymer-clad TSVs                                                                                                                                                                                                                                                                                                  | 26 |

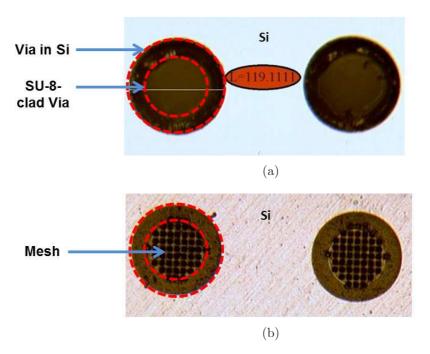

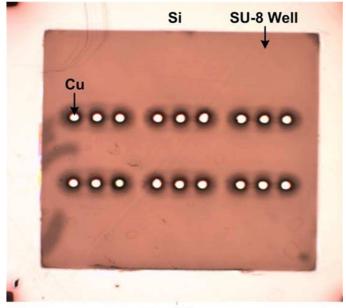

| 16 | Fabricated 390 $\mu$ m tall SU-8-clad vias with $\sim$ 80 $\mu$ m diameter openings and $\sim$ 20 $\mu$ m thick cladding on a 250 $\mu$ m pitch: (a) Top view and (b) Base view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

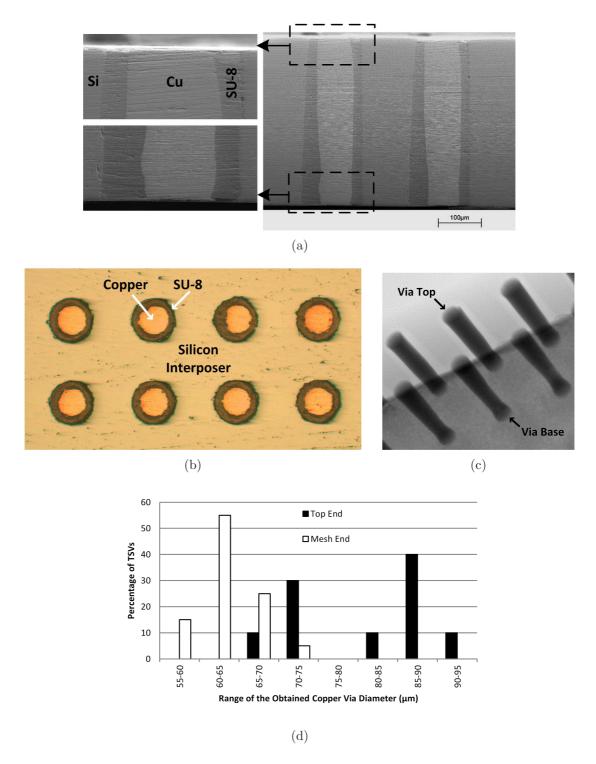

| 17 | Fabricated 390 $\mu$ m tall SU-8-clad TSVs with $\sim 80~\mu$ m diameter copper vias surrounded by a $\sim 20~\mu$ m thick cladding on a 250 $\mu$ m pitch: (a) Cross section view; (b) Top view; (c) X-ray image showing void-free copper electroplating; and (d) Distribution of the obtained copper via diameters of 20 measured polymer-clad TSVs                                                                                                                                                                                                                                                                                                                                                                                                                               | 28 |

| 18 | Fabrication process for simultaneous fabrication of photodefined optical and polymer-clad TSVs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29 |

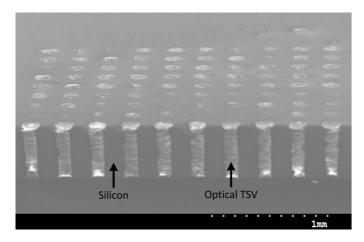

| 19 | Fabricated 390 $\mu$ m tall optical TSVs with a 118 $\mu$ m diameter SU-8 core surrounded by a 2 $\mu$ m thick silicon dioxide cladding on a 250 $\mu$ m pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30 |

| 20 | SU-8 filling experiments for vias in silicon with a silicon dioxide layer at the base: (a) 120 $\mu$ m diameter and 200 $\mu$ m tall vias on a 250 $\mu$ m pitch in silicon after SU-8 dispensing, a 6 hour wait and soft bake; (b) A silicon sample with 120 $\mu$ m diameter and 200 $\mu$ m tall vias on a 250 $\mu$ m pitch after SU-8 dispensing and vacuum processing; (c) 120 $\mu$ m diameter and 200 $\mu$ m tall vias on a 250 $\mu$ m pitch in silicon after SU-8 dispensing, heat treatment in a vacuum oven, vacuum processing in the oven, cooling and soft bake; and (d) 30 $\mu$ m diameter and 300 $\mu$ m tall vias on a 60 $\mu$ m pitch in silicon after SU-8 dispensing, heat treatment in a vacuum oven, vacuum processing in the oven, cooling and soft bake | 32 |

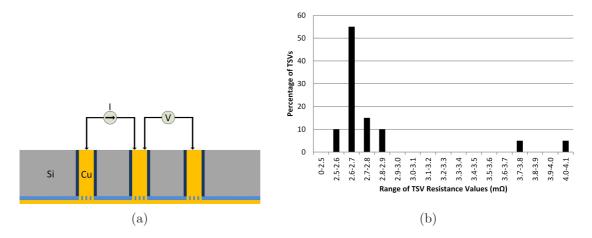

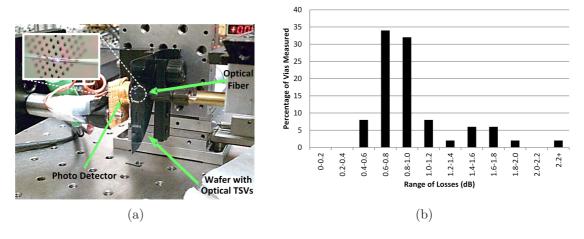

| 21 | Four-point resistance measurements of the fabricated polymer-clad TSVs: (a) Four-point resistance measurement setup and (b) Distribution of the measured resistance values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34 |

| 22 | Optical loss measurements for the fabricated optical TSVs: (a) Setup to measure optical loss of the fabricated optical TSVs with an inset image showing optical fiber in contact with an optical TSV and (b) Distribution of the measured optical losses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

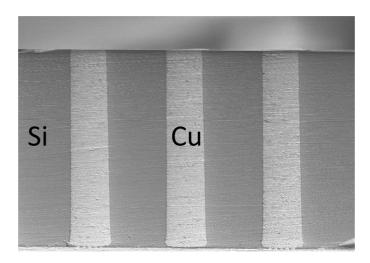

| 23 | Fabricated 50 $\mu m$ diameter and 300 $\mu m$ tall TSVs with 1 $\mu m$ thick silicon dioxide liner and on a 150 $\mu m$ pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38 |

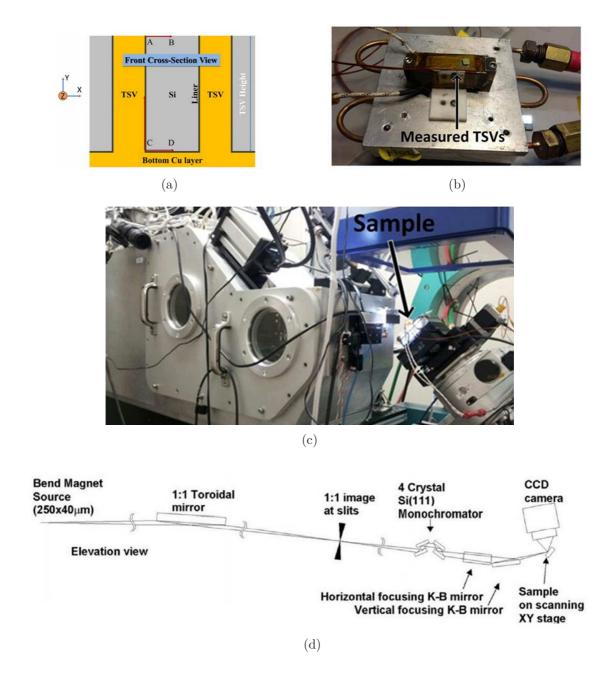

| 24 | Synchrotron XRD setup for TSV strain measurements: (a) Schematic of the TSV area measured; (b) Setup of a TSV sample attached to a heater; (c) Beamline setup with the TSV sample; and (d) Schematic layout of the beamline [74].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39 |

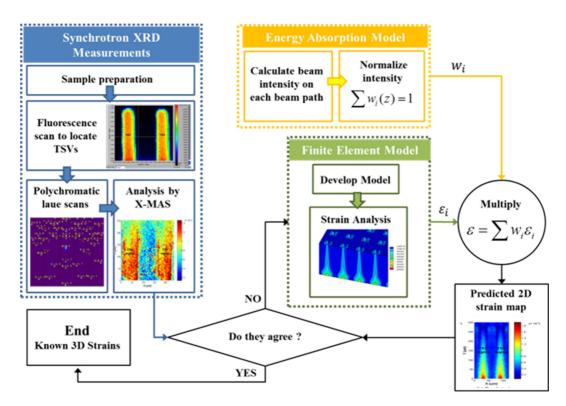

| 25 | Beam intensity based data averaging method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40 |

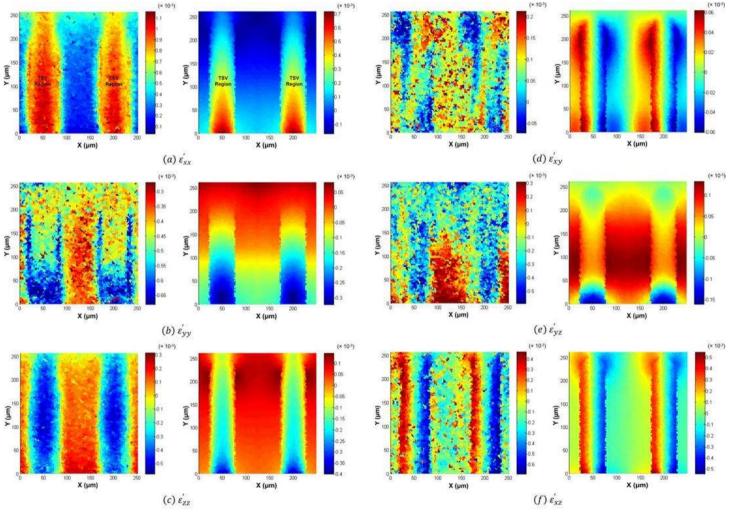

| 26 | Measured deviatoric strain distribution maps of silicon (left) vs. model predicted strain maps (right) at 150 °C for the fabricated 50 $\mu$ m diameter and 300 $\mu$ m tall TSVs with 1 $\mu$ m thick silicon dioxide liner and on a 150 $\mu$ m pitch                                                                                                                                                                                         | 41 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

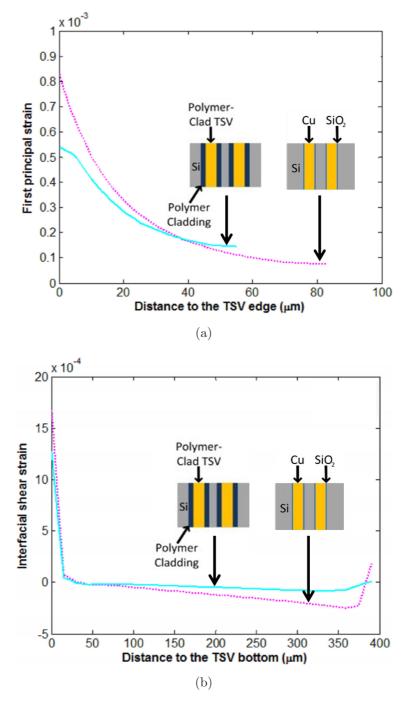

| 27 | At 150 °C, predicted (a) first principal strain of silicon at the top of TSVs along the path stretching radially away from the liner-silicon interface and (b) interfacial shear strain along copper/liner interface.                                                                                                                                                                                                                           | 43 |

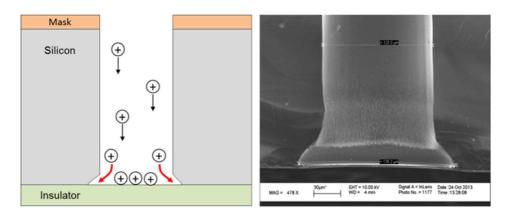

| 28 | Notching mechanism in TSV fabrication using BOSCH process (Left) and cross-section of a 120 $\mu$ m diameter via showing notching at the base (Right)                                                                                                                                                                                                                                                                                           | 44 |

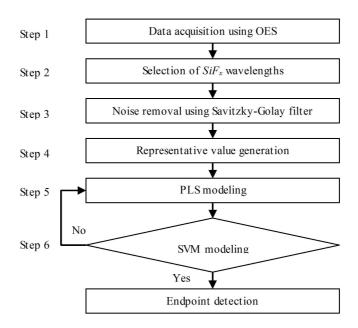

| 29 | Flowchart of the proposed PLS-SVM model                                                                                                                                                                                                                                                                                                                                                                                                         | 46 |

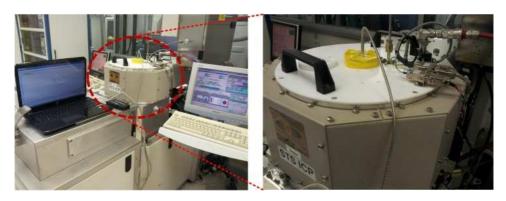

| 30 | OES setup with sensor mounted on top of ICP etching tool process chamber (closer image shown on the right)                                                                                                                                                                                                                                                                                                                                      | 46 |

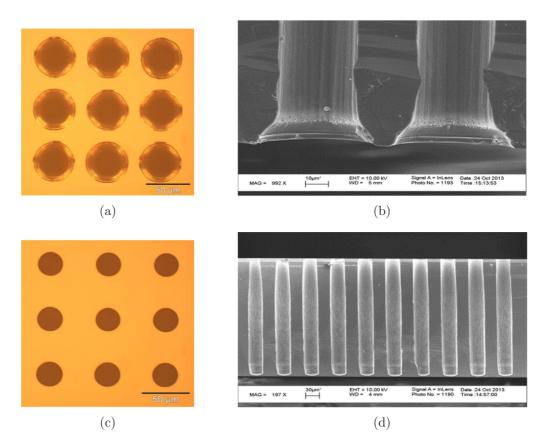

| 31 | Etching results for 300 $\mu$ m tall vias with $\sim 25~\mu$ m diameter for EPD: (a) Optical image from base of the vias for the first half of a wafer; (b) SEM image of via cross section for the first half of the wafer; (c) Optical image from base of the vias for the second half of the wafer; (d) SEM image of via cross section for the second half of the wafer; and (e) Summary of the TSV etching results for the two wafer halves. | 47 |

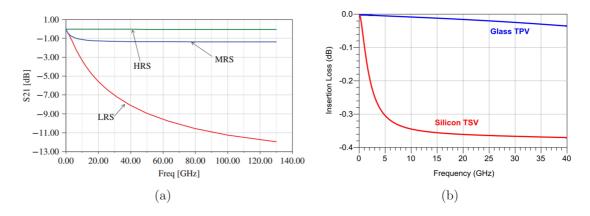

| 32 | Losses of copper vias (a) in high-resistivity silicon with 75 $\mu$ m diameter and 300 $\mu$ m tall copper vias with a 0.6 $\mu$ m thick silicon dioxide liner [86], and (b) in glass substrate with 15 $\mu$ m diameter and 30 $\mu$ m tall copper vias and in 10 S/m conductivity silicon with 15 $\mu$ m diameter and 50 $\mu$ m tall copper vias with a 0.5 $\mu$ m thick silicon dioxide liner [85].                                       | 50 |

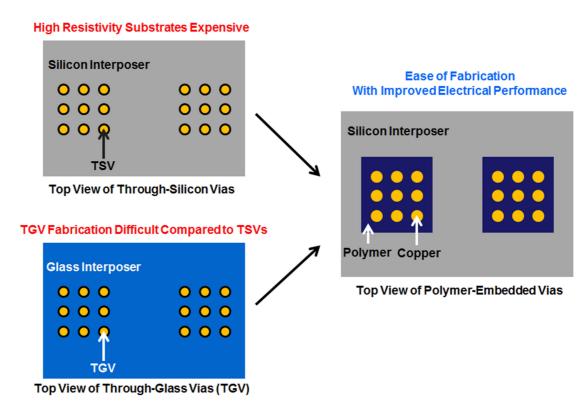

| 33 | Comparison between through-silicon vias, through-glass vias and polymer-embedded vias                                                                                                                                                                                                                                                                                                                                                           | 51 |

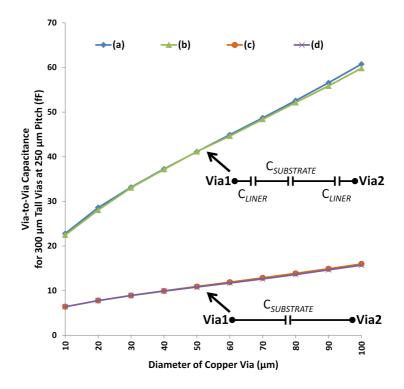

| 34 | Via-to-via capacitance for passive silicon interposers: (a) Using the model for TSVs with a 1 m thick silicon dioxide liner; (b) Using Raphael simulations for TSVs with a 1 $\mu$ m thick silicon dioxide liner; (c) Using the model for polymer-embedded vias; and (d) Using Raphael simulations for polymer-embedded vias                                                                                                                    | 53 |

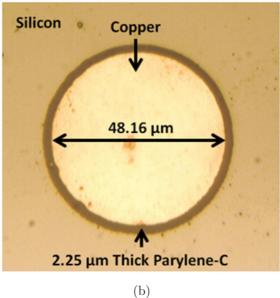

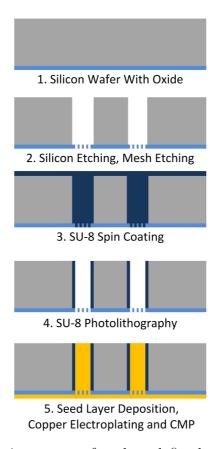

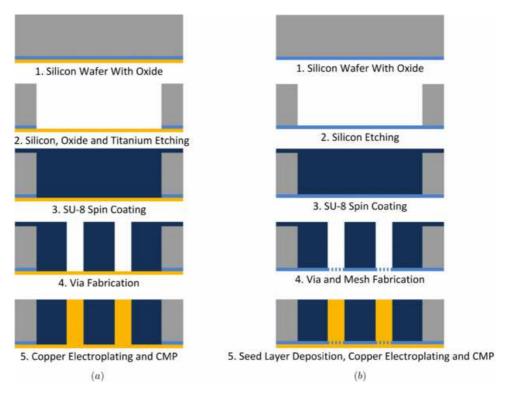

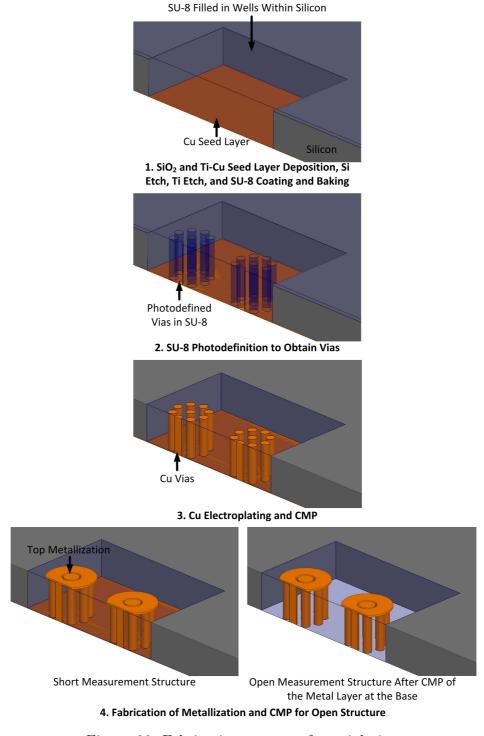

| 35 | Fabrication processes for polymer-embedded vias: (a) Process with copper support layer and (b) Process with mesh seed layer                                                                                                                                                                                                                                                                                                                     | 55 |

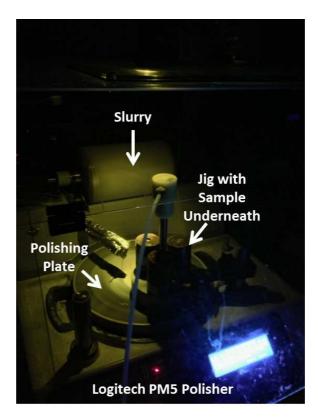

| 36 | An image of the setup used to polish uncrosslinked SU-8 in an ultra-low light environment                                                                                                                                                                                                                                                                                                                                                       | 56 |

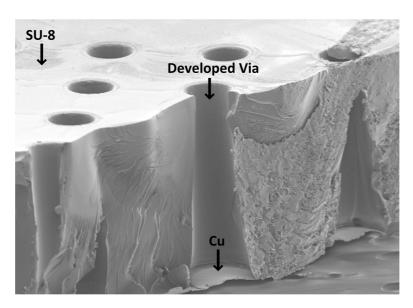

| 37 | Cross section of a polymer-embedded via after SU-8 development                                                                                                                                                                                                                                                                                                                                                                                  | 57 |

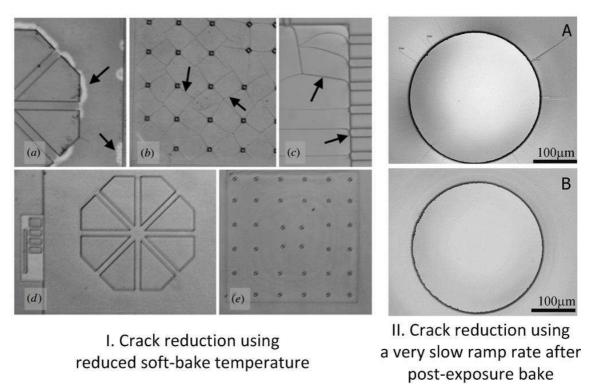

| 38 | Crack reduction techniques demonstrated in the literature [93–94]                                                                                                                                                                                                                                                                                                                                                                               | 58 |

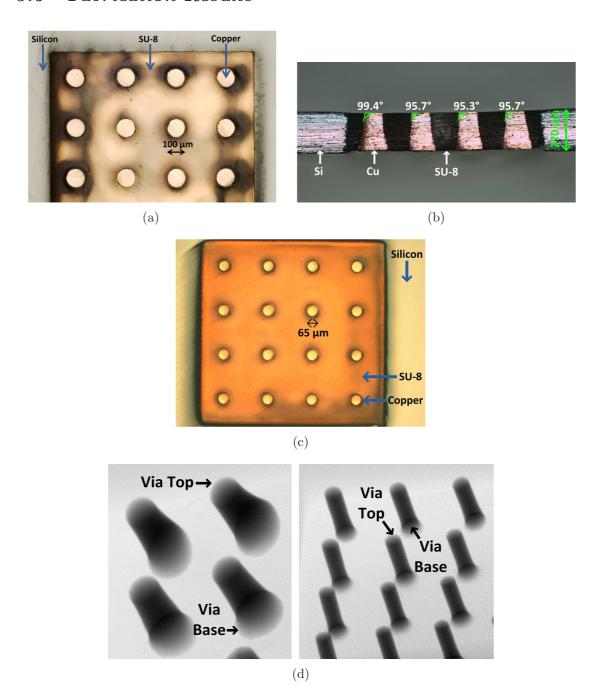

| 39 | Fabricated 270 $\mu$ m tall polymer-embedded vias on a 250 $\mu$ m pitch:<br>(a) Top view of 100 $\mu$ m diameter TSVs; (b) Cross-section view of the 100 $\mu$ m diameter TSVs; (c) Top view of 65 $\mu$ m diameter TSVs; and (d) X-ray image showing void-free copper electroplating of the 100 $\mu$ m diameter TSVs (left) and the 65 $\mu$ m diameter TSVs (right)                                                                                                                    | 61 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 40 | Fabricated 370 $\mu$ m tall polymer-embedded vias on a 150 $\mu$ m pitch: (a) Top view and (b) Cross-section view                                                                                                                                                                                                                                                                                                                                                                          | 63 |

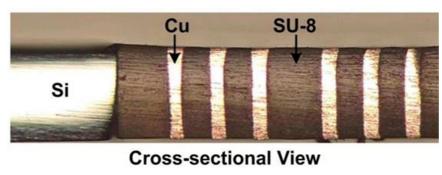

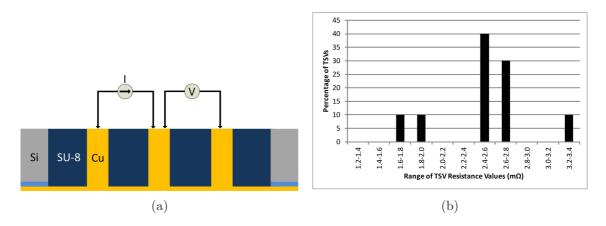

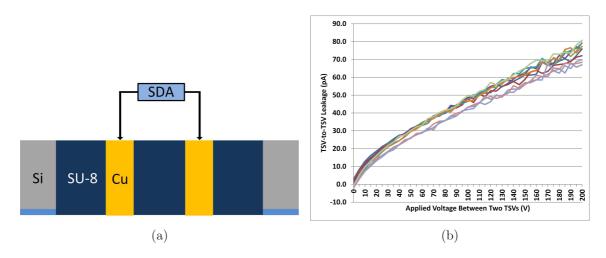

| 41 | Resistance measurements of polymer-embedded vias with 100 $\mu$ m diameter and 270 $\mu$ m height: (a) Schematic of 4-point resistance measurement setup and (b) Distribution of 4-point resistance measurements for 20 polymer-embedded vias                                                                                                                                                                                                                                              | 64 |

| 42 | Via-to-via leakage measurement of polymer-embedded vias with 100 $\mu$ m diameter and 270 $\mu$ m height: (a) Schematic of leakage measurement setup and (b) Leakage measurements of 10 pairs of polymer-embedded vias                                                                                                                                                                                                                                                                     | 64 |

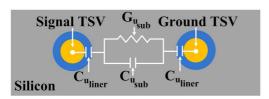

| 43 | Top view of $RLCG$ schematic for signal-ground TSV pairs                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66 |

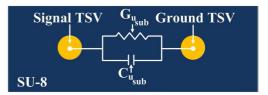

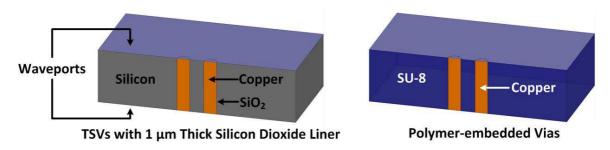

| 44 | HFSS simulation structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 69 |

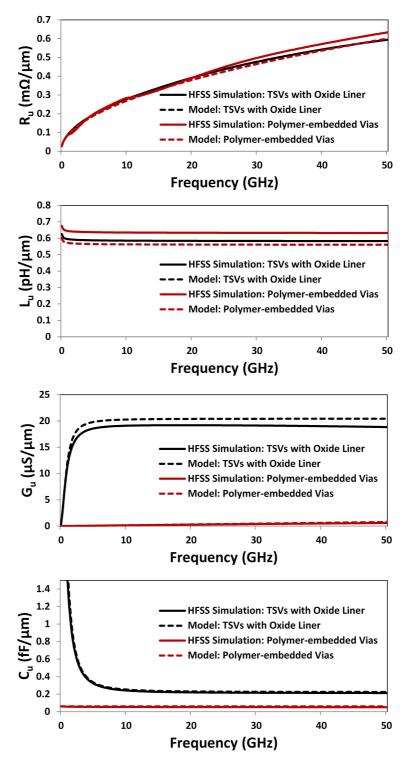

| 45 | Evaluated per-unit-length TSV $RLGC$ values using circuit models and HFSS simulations                                                                                                                                                                                                                                                                                                                                                                                                      | 70 |

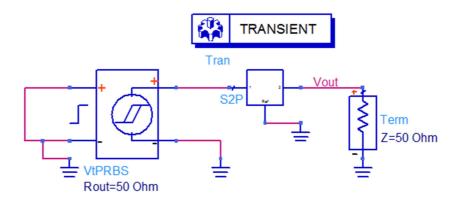

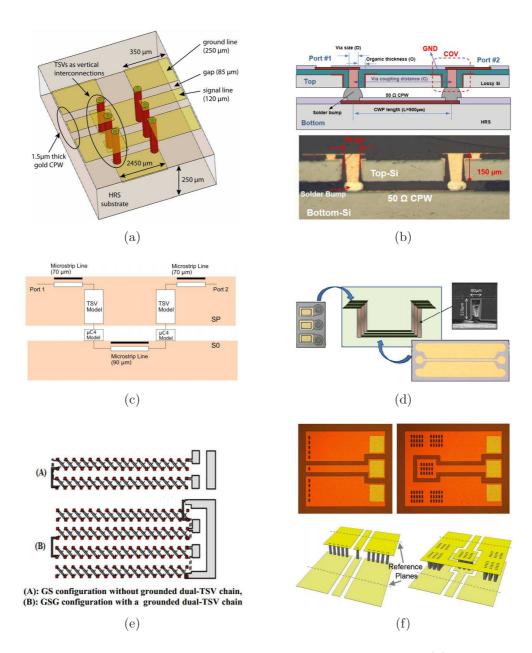

| 46 | ADS schematic setup for eye diagrams of TSVs                                                                                                                                                                                                                                                                                                                                                                                                                                               | 72 |

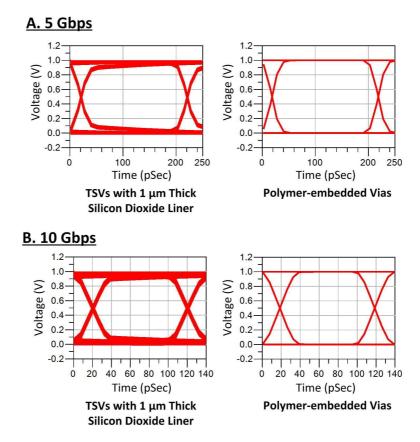

| 47 | Eye diagrams of TSVs with silicon dioxide liner and polymer-embedded vias                                                                                                                                                                                                                                                                                                                                                                                                                  | 72 |

| 48 | TSV RF measurement structures in the literature for: (a) TSVs with gold coated nickel wires assembled magnetically [106]; (b) coaxial structures with laser ablated polymer-filled vias [84]; (c) TSV loss characterization in CMOS SOI technology [104]; (d) characterization of TSVs in high-resistivity silicon for RF interposer applications [107]; (e) characterization of tungsten-filled dual-TSV chains [102]; and (f) implementation of TRL de-embedding using TSV bundles [108] | 73 |

| 49 | TSV RF measurement setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 74 |

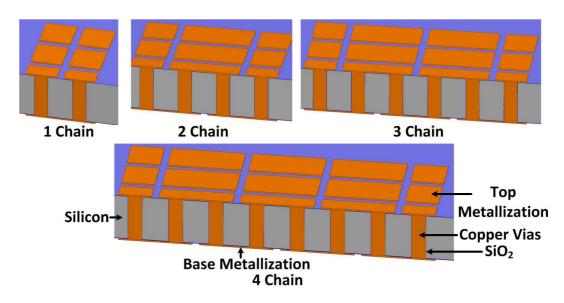

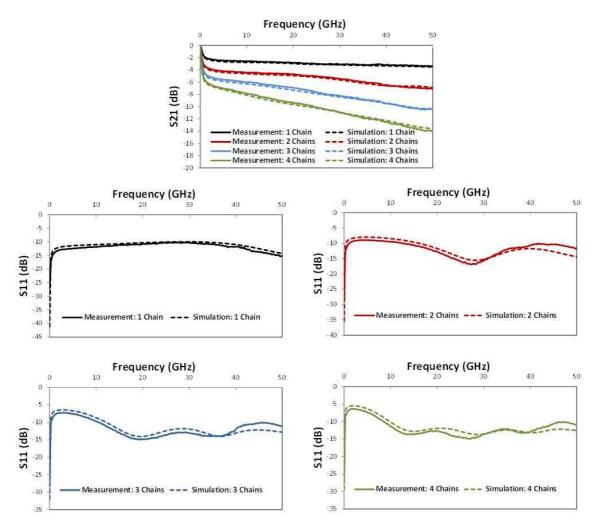

| 50 | Structures simulated in HFSS for chains of TSVs with silicon dioxide liner                                                                                                                                                                                                                                                                                                                                                                                                                 | 75 |

| 51 | Fabricated chains of TSVs with silicon dioxide liner                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75 |

| 52 | RF measurements and simulations of TSVs with silicon dioxide liner.                                                                                                                                                                                                                                                                                                                                                                                                                        | 76 |

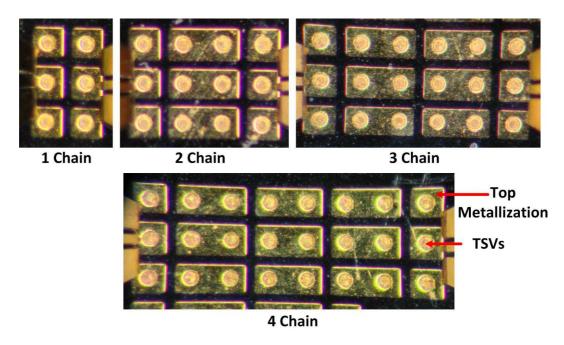

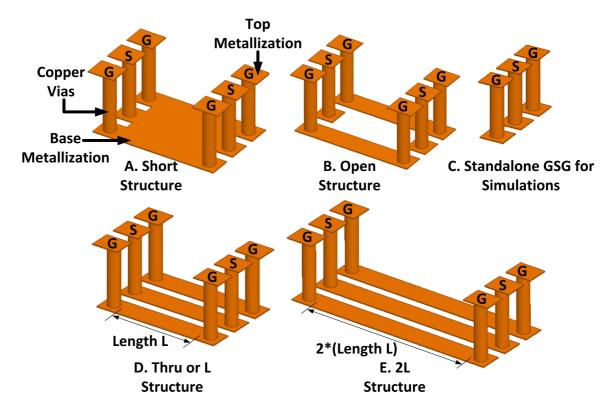

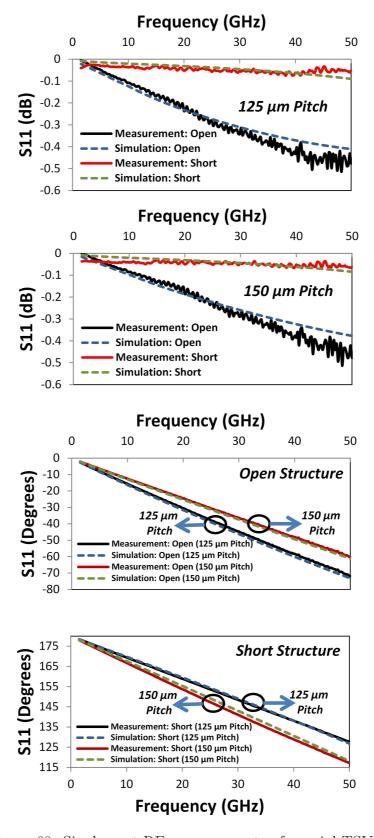

| 53 | Schematic of measured and simulated TSV structures for de-embedding.                                                                                                                                                                                                                                                                                                                                                                                                                       | 79 |

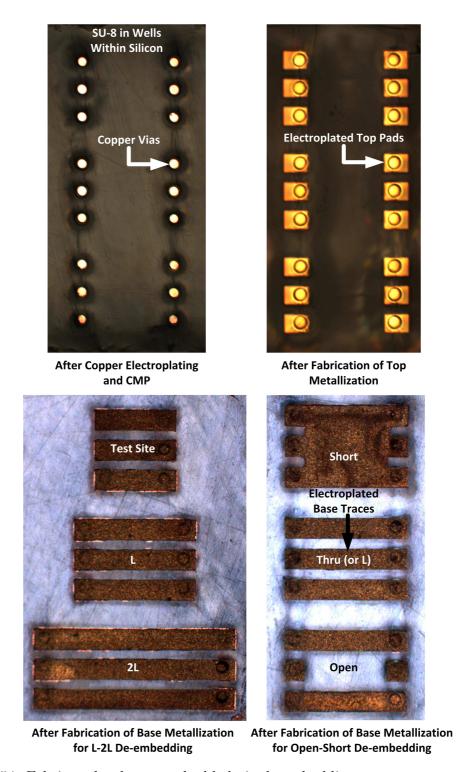

| 54 | Fabricated polymer-embedded via de-embedding measurement structures                                                                                                                                                                                                                                      | 80  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

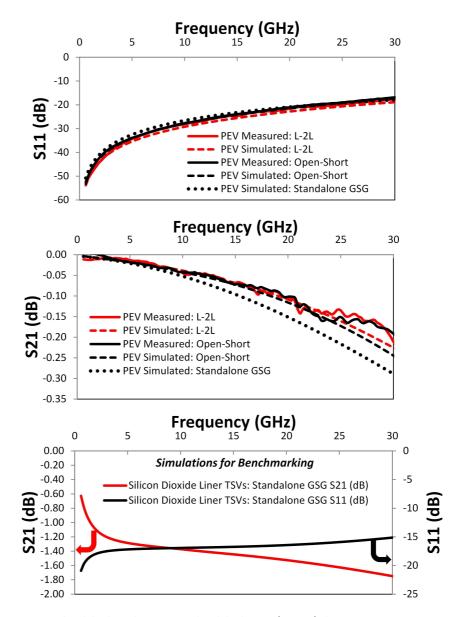

| 55 | De-embedded polymer-embedded via (PEV) loss using measurements and simulations; TSVs with silicon dioxide liner included for benchmarking                                                                                                                                                                | 82  |

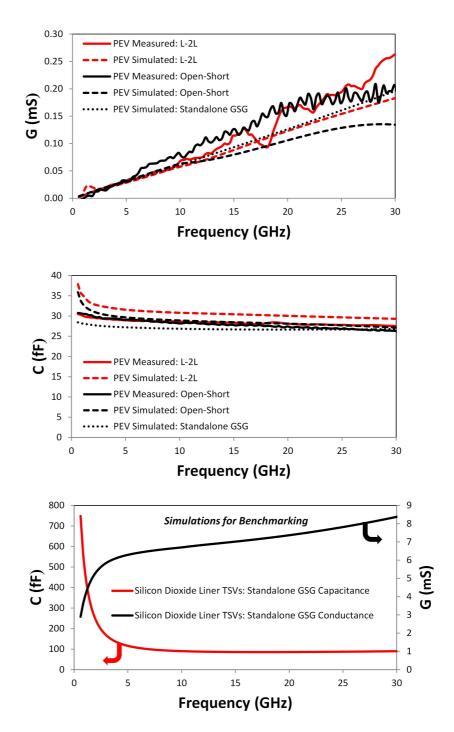

| 56 | Extracted conductance and capacitance of the de-embedded polymer-embedded vias (PEVs) using measurements and simulations; TSVs with silicon dioxide liner included for benchmarking                                                                                                                      | 83  |

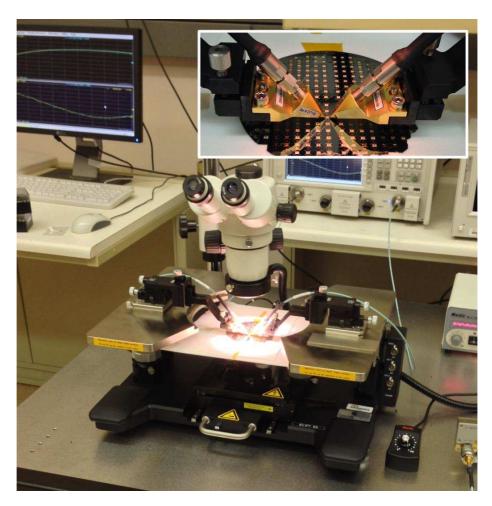

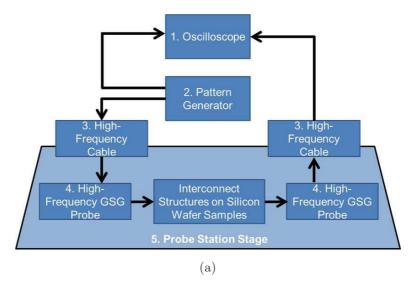

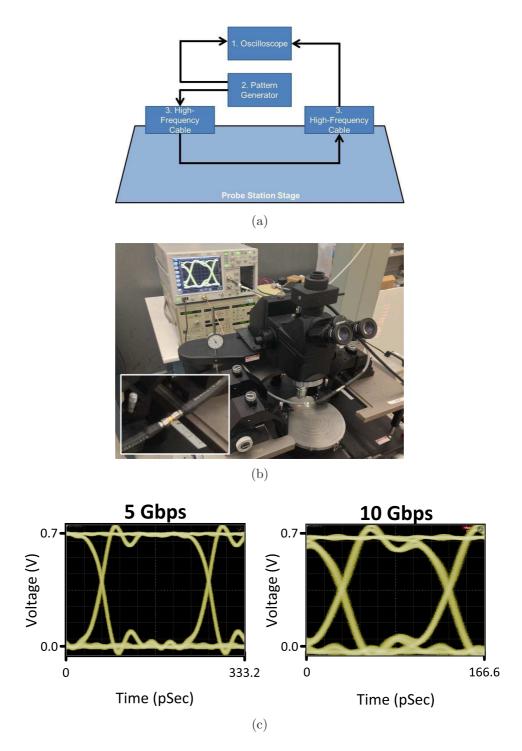

| 57 | TSV time-domain measurement setup: (a) Schematic and (b) The measurement setup                                                                                                                                                                                                                           | 84  |

| 58 | Time-domain loopback characterization (a) schematic, (b) measurement setup, and (c) measurements                                                                                                                                                                                                         | 86  |

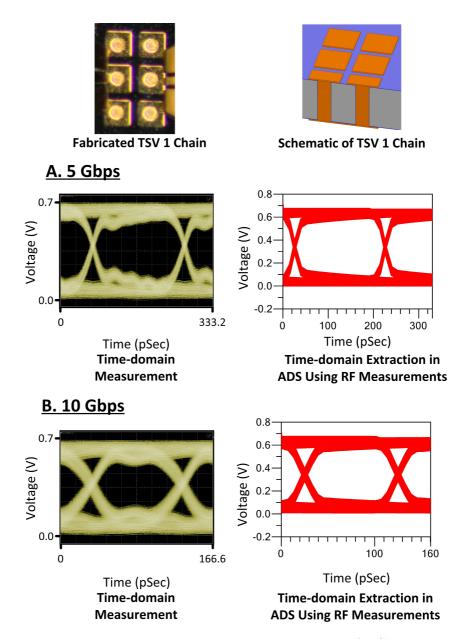

| 59 | Time-domain measurements and extractions in ADS using RF measurements for TSV 1 chain                                                                                                                                                                                                                    | 87  |

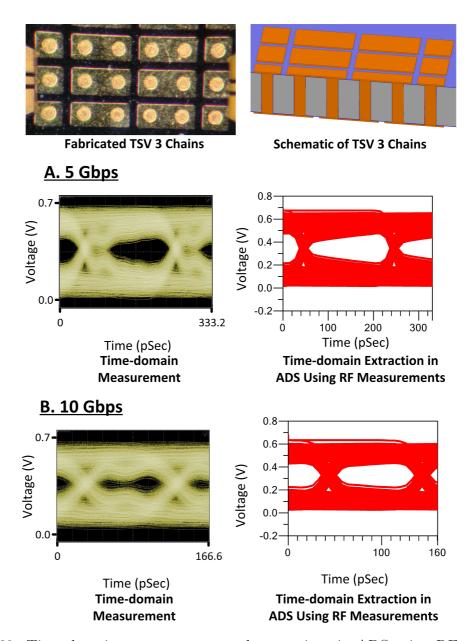

| 60 | Time-domain measurements and extractions in ADS using RF measurements for TSV 3 chains                                                                                                                                                                                                                   | 88  |

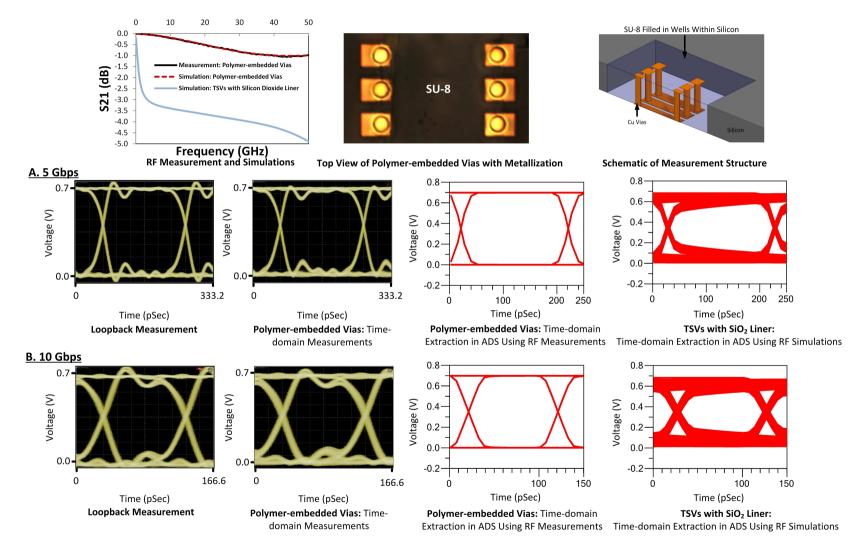

| 61 | Measured eye diagrams of polymer-embedded vias (Figure 54) with constructed eye diagrams in ADS using the RF measurements of polymer-embedded via chains. Loopback measurement and extracted eye diagrams from the RF simulations of the TSVs with silicon dioxide liner are also shown for benchmarking | 89  |

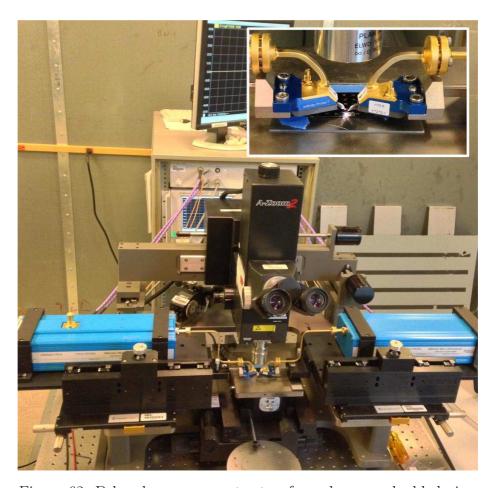

| 62 | D-band measurement setup for polymer-embedded vias                                                                                                                                                                                                                                                       | 90  |

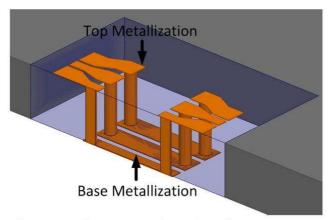

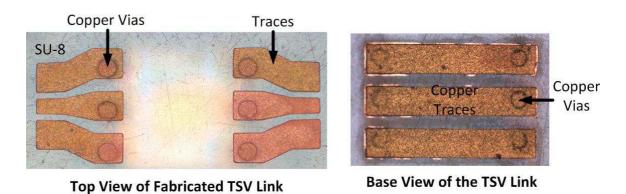

| 63 | Fabricated polymer-embedded vias for measurements in the D band including traces with fan-in at top                                                                                                                                                                                                      | 91  |

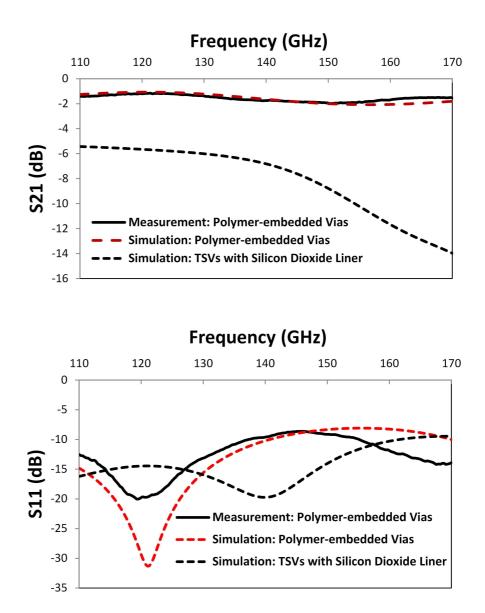

| 64 | D-band measurements and simulations of a polymer-embedded via link; TSVs with silicon dioxide liner included for benchmarking                                                                                                                                                                            | 92  |

| 65 | Envisioned mixed-signal silicon interposer platform featuring polymerenhanced TSVs, antennas and inductors                                                                                                                                                                                               | 95  |

| 66 | Fabrication process of coaxial vias                                                                                                                                                                                                                                                                      | 97  |

| 67 | Fabricated coaxial vias for 1-port measurements                                                                                                                                                                                                                                                          | 98  |

| 68 | Single-port RF measurements of coaxial TSVs                                                                                                                                                                                                                                                              | 99  |

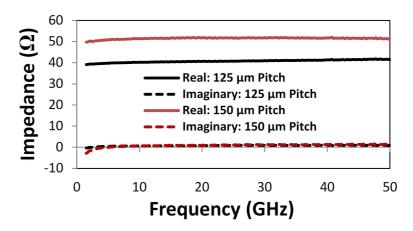

| 69 | Extracted impedance from the coaxial TSV measurements                                                                                                                                                                                                                                                    | 100 |

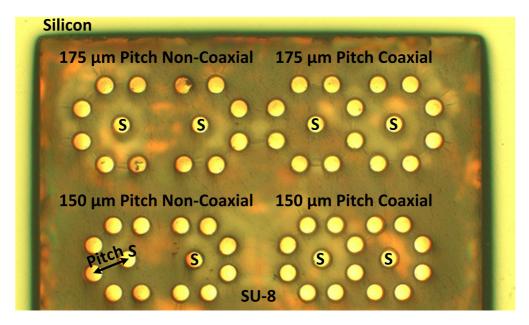

| 70 | Fabricated polymer-enhanced coaxial vias and non-coaxial vias (for benchmarking)                                                                                                                                                                                                                         | 101 |

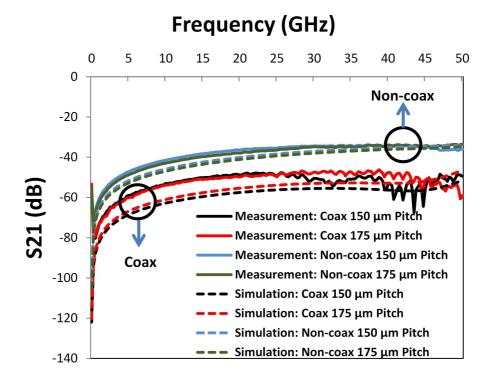

| 71 | and non-coaxial TSVs                                                                                                                       | 102 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 72 | Fabrication process of polymer-enhanced antennas                                                                                           | 105 |

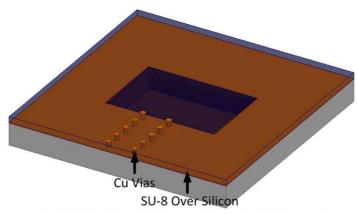

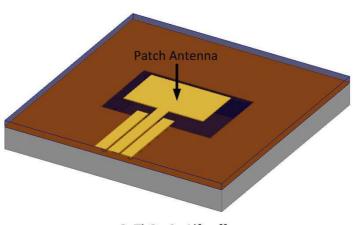

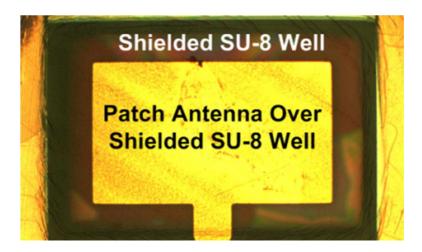

| 73 | Fabricated patch antenna over a metal-coated polymer well                                                                                  | 106 |

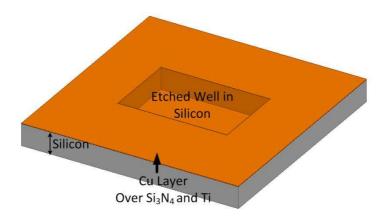

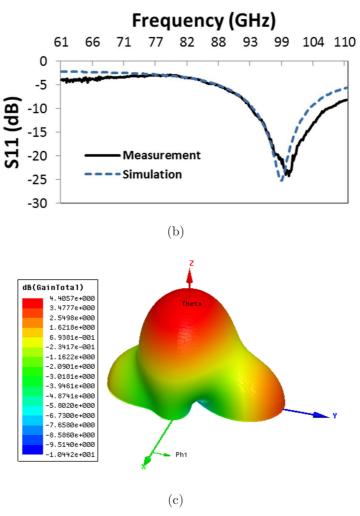

| 74 | Antenna measurement and simulations: (a) Setup; (b) One-port measurement and simulation; and (c) Radiation pattern simulation at 100 GHz   | 107 |

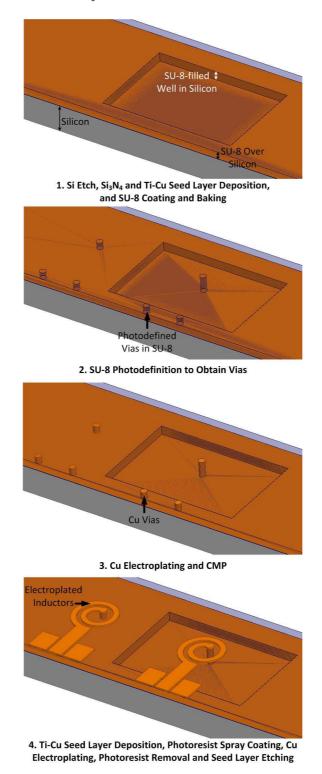

| 75 | Fabrication process of polymer-enhanced inductors                                                                                          | 110 |

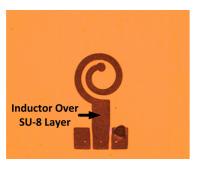

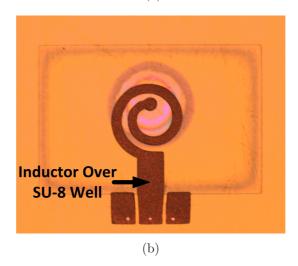

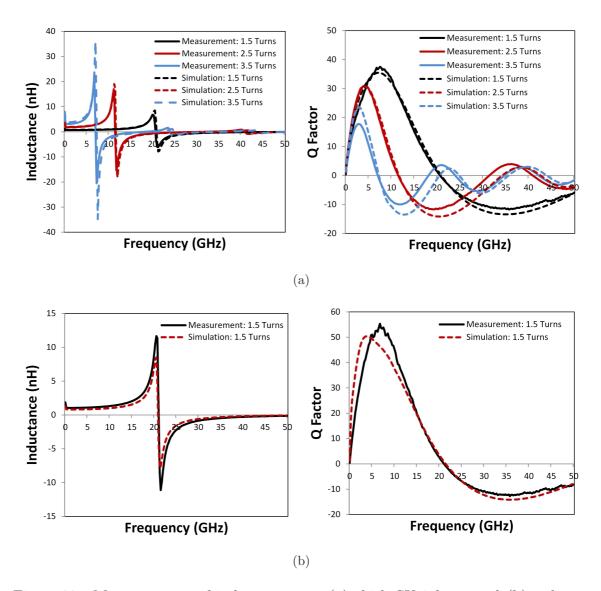

| 76 | Fabricated inductors over: (a) thick SU-8 layer and (b) polymer well.                                                                      | 112 |

| 77 | Measurements of inductors over: (a) thick SU-8 layer and (b) polymer well                                                                  | 113 |

| 78 | Proposed RF/mixed-signal large-scale interposer-based system with the key components demonstrated in this research for the system. $\dots$ | 116 |

| 79 | Summary of the proposed future work                                                                                                        | 118 |

| 80 | Fabricated suspended SU-8 wells.                                                                                                           | 121 |

### **SUMMARY**

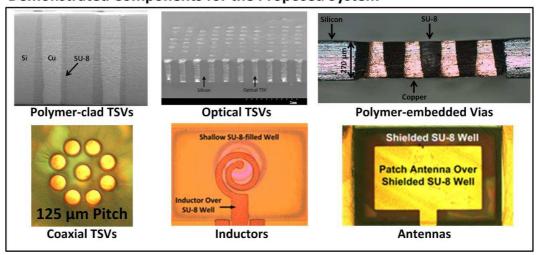

Novel polymer-enhanced photodefined through-silicon via (TSV) and passive technologies have been demonstrated for silicon interposers to obtain compact heterogeneous computing and mixed-signal systems. These technologies include: (1) Polymer-clad TSVs with thick ( $\sim$ 20  $\mu$ m) liners to help reduce TSV losses and stress, and obtain optical TSVs in parallel for interposer-to-interposer long-distance communication; (2) Polymer-embedded vias with copper vias embedded in polymer wells to significantly reduce the TSV losses; (3) Coaxial vias in polymer wells to reduce the TSV losses with controlled impedance; (4) Antennas over polymer wells to attain a high radiation efficiency; and (5) High-Q inductors over polymer wells.

Cleanroom fabrication and characterization of the technologies have been demonstrated. For the fabricated polymer-clad TSVs, resistance and synchrotron x-ray diffraction (XRD) measurements have been demonstrated. High-frequency measurements up to 170 GHz and time-domain measurements up to 10 Gbps have been demonstrated for the fabricated polymer-embedded vias. For the fabricated coaxial vias and inductors, high-frequency measurements up to 50 GHz have been demonstrated. Lastly, for the fabricated antennas, measurements in the W-band have been demonstrated.

### CHAPTER I

#### INTRODUCTION

The information revolution, fueled by the development of computing and communication technologies, has significantly improved our lives and promises to provide a world of highly interconnected devices. By 2020, more than 30 billion devices are estimated to be connected to the internet and the amount of digital data in this interconnected world is estimated to be greater than 40 zettabytes (10<sup>21</sup> bytes) [1]. This enormous rise of interconnected devices and digital data demands high-performance systems with faster connectivity and data storage. To cope with these demands, significant technology innovations are highly desired.

This research focuses on the development of photodefined polymer-enhanced interconnection and passive technologies to enable compact heterogeneous computing and mixed-signal systems. The motivation for the development of these components is described next.

#### 1.1 Motivation

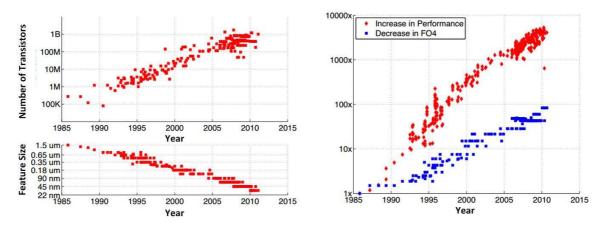

Since the invention of the transistor in 1947, the information revolution has been consistently driven by semiconductor technology innovations. The integrated circuit (IC), invented in 1958, has been the key technology fueling the revolution owing to its constant improvements in productivity and performance [2]. Following Gordon Moore's projection in 1965 [3], the number of transistors in a given area has continually increased with device scaling, as shown in Figure 1 [4]. This increase in the number of transistors has been a key factor in reducing gate cost and leading to affordable ICs with more functionality and thereby significantly improved productivity. Moreover, the performance of microprocessor ICs has increased by more than

3000X while the gate speeds have increased by more than 100X since the mid-1980s when complementary metal-oxide semiconductor (CMOS) microprocessors were introduced [4]. To sustain the continued improvement in microprocessor performance while limiting power dissipation, multicore microprocessors have been implemented since the early 2000s instead of aggressive clock frequency scaling [5–7]. However, the migration to multicore microprocessors has created an incredible demand for low-energy and high-bandwidth off-chip communication [8].

Figure 1: Consistent increase in transistor count, consistent transistor scaling, and improvements in microprocessor performance (normalized to that of a 386) and gate speeds (approximation of the FO4) since the introduction of CMOS microprocessors [4].

#### 1.1.1 Demand for High Off-chip Bandwidth

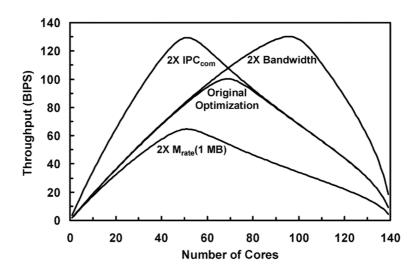

K. Bowman et al. [9] have demonstrated that increasing the communication bandwidth greatly improves throughput for a system with a many-core CPU and memory (Figure 2) using the following equation:

$$TP(N) = \frac{N}{\frac{CPI_{com}}{F_{clk}} + \frac{CPI_{mem,lat}(F_{clk})}{F_{clk}} + \frac{CPI_{mem,bw}(F_{clk})}{F_{clk}}},$$

(1)

where N represents the number of cores,  $F_{clk}$  the clock frequency,  $CPI_{com}$  the computation component of cycles per instruction (CPI),  $CPI_{mem,lat}$  the memory latency component of CPI, and  $CPI_{mem,bw}$  the bandwidth component of CPI.

Figure 2: Plot showing performance improvement in a many-core chip with high memory bandwidth [9].

Equation 1 shows that to improve the system throughput, the memory bandwidth must be improved in addition to reducing memory latency (which includes interconnect and memory access delays). As the memory bandwidth increases, the cache size constraints are lowered thus allowing for more cores in the same area resulting in higher performance.

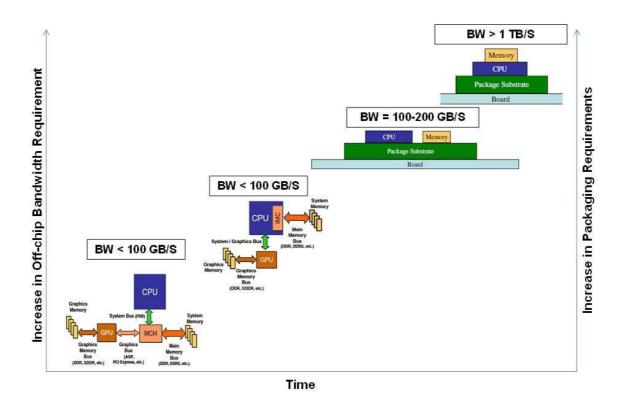

Moreover, Figure 3 qualitatively shows the increasing off-chip bandwidth demands, due first of all to the integration of the memory controller hub in the CPU, and then to the transition to multi-core microprocessors, requiring innovative interconnection and packaging solutions.

#### 1.1.2 Demand for Heterogeneous Integration Platforms

In addition to the digital circuits, analog and radio-frequency (RF) functionalities are highly desired for high-performance and high-speed computing and communication systems. This need for the integration of different functionalities has led to the development of heterogeneous platforms such as system-on-chip (SoC) architectures [10]. However, there are challenges with the heterogeneous integration platforms as described next.

Figure 3: Increase in off-chip bandwidth and demand for innovative interconnection and packaging technologies. Images in the plot are from L. Polka et al. [8].

#### 1.1.2.1 Analog and Radio-frequency IC Integration

Unlike digital circuits, the performance and precision of analog systems have not been significantly improving due to scaling. Instead, scaled MOS transistors worsen matching and noise, while a reduction of the supply voltage affects signal energy and signal-to-noise ratios [11]. Moreover, with respect to RF systems, power amplifiers (a critical building block in wireless systems) are traditionally implemented using III-V heterojunction bipolar transistor (HBT) based solutions for performance and cost effectiveness [12]. Hence, significantly different requirements must be met by a platform such as SoC for the integration of heterogeneous technologies.

## 1.1.2.2 Integration of Passives

Additionally, for RF and analog/mixed-signal (AMS) systems, the implementation of high-performance on-chip passive components such as inductors is highly desired,

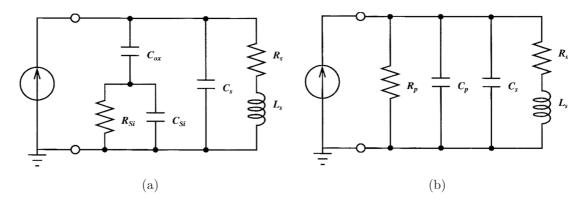

although very challenging [10]. This need for the integration of passives has been a key barrier to the scaling of RFICs, including power amplifiers, voltage controlled oscillators and filters [13]. For example, on-chip inductors in CMOS processes yield poorer Q-factors (<30) compared to off-chip inductors due to high-frequency losses in silicon and ohmic losses in metal layers [14]. To explain this more clearly, a 2D planar inductor (a spiral inductor, for example) model with one-port excitation over silicon and an oxide layer between the inductor and the silicon is shown in Figure 4(a) [15].

Figure 4: Inductor physical models: (a) Lumped model and (b) Equivalent circuit model using the lumped model [15].

In the series path of the inductor,  $L_s$  represents the spiral inductance,  $R_s$  the metal series resistance, and  $C_s$  the capacitance due to the overlaps between the spiral and the center-tap underpass. The parasitics in the shunt path include  $C_{ox}$  representing the oxide capacitance between the spiral and the substrate,  $C_{Si}$  the silicon substrate capacitance, and  $R_{Si}$  the silicon substrate resistance. Converting the shunt path into  $R_p$  and  $C_p$  in parallel, an equivalent circuit model is obtained, as shown in Figure 4(b). From the equivalent circuit model, the Q-factor for the inductor is obtained as follows [15]:

$$Q = \frac{\omega L_s}{R_s} * \frac{R_p}{R_p + \left[ \left( \frac{\omega L_s}{R_s} \right)^2 + 1 \right] R_s} * \left[ 1 - \frac{R_s^2 (C_s + C_p)}{L_s} - \omega^2 L_s (C_s + C_p) \right], \quad (2)$$

where Equation 2 could be rewritten as

$$Q = \frac{\omega L_s}{R_s} * \text{substrate loss factor} * \text{self-resonance factor}.$$

(3)

In the Equations 2 and 3,  $\omega L_s/R_s$  represents the magnetic energy stored and the ohmic loss in the series resistance. The other two components of the Q-factor are represented by the substrate loss factor and the self-resonance factor. At low frequencies, the Q-factor depends on  $\omega L_s/R_s$  and at higher frequencies it primarily depends on the substrate loss factor. The equation for the substrate loss factor shows that with a very high  $R_p$  the loss factor approaches unity resulting in a significant reduction in the impact of the substrate loss on the Q-factor. Consequently, the Q-factor can be improved by reducing the parallel conductance. Typically, this is accomplished with techniques such as high-resistivity silicon or removing silicon from the back side of a chip [16, 17], but these options could be expensive at chip level.

Moreover, according to the International Technology Roadmap for Semiconductors (ITRS), Q-factors greater than 50 will be needed beyond 2020 [10]. This requirement suggests a need for high-performance off-chip inductors that can be integrated close to ICs with minimal impact from the interconnect parasitics.

#### 1.1.2.3 Integration of Antennas and Millimeter-wave Applications

Similar to inductors, the performance of on-chip antennas suffers from losses in silicon yielding low gains (<-2 dBi) [18]. This low-gain performance results because on-chip antennas find a low-resistivity path through the silicon substrate and the high dielectric constant of the silicon substrate causes most of the antenna power to be confined in the substrate [18]. Moreover, antennas built on CMOS or SiGe have very narrow impedance and gain bandwidths [19].

The poor on-chip antenna performance has consequently created a demand for the integration of off-chip antennas close to ICs for a wide range of applications, specifically for those in the millimeter-wave (mm-wave) frequency bands (30 GHz - 300 GHz) with smaller antenna sizes. For example, the frequency band around 60 GHz has been explored for high-speed multimedia transfer and short-range communications [20]; the band around 28 GHz has been explored for the future 5G communications [21]; the band around 77 GHz has been explored for radars in automobiles [22]; and the D-band has been explored for medical imaging and pico-cell cellular links [23]. For these applications the integration of heterogeneous ICs, inductors and antennas on a platform with short distance communication between them is highly desired.

#### 1.1.3 Interposers for Heterogeneous Integration

To cope with these demands, 2.5-dimensional (2.5D) interconnection of microelectronic circuits is currently being extensively explored [24–31]. Compared to multichip modules with chips over ceramic or organic substrates, 2.5D integration is enabled by interposers with fine-pitch wiring and vertical through-substrate vias supporting multiple chips. Silicon, glass and organic substrates have chiefly been explored in the literature for interposers with a second level package in between them and motherboard [31–33]. However, silicon interposers (as shown in Figure 5) have clear advantages over glass and organic interposers: (1) a denser metallization can be obtained over silicon interposers with relative ease using conventional back-end-of-line (BEOL) processing techniques; (2) silicon has better thermal conductivity; and (3) the fabrication of through-silicon vias (TSVs) and fine-pitch microbumps is becoming well established. These advantages enable high bandwidth-density communication between the chips mounted over silicon interposers (using a comparatively simpler fabrication) [29]. Additionally, silicon interposers provide opportunities for the integration of antennas and inductors close to ICs, yielding compact RF and AMS systems. The TSVs, with copper conductors insulated from the silicon commonly using a thin ( $<1 \mu m$ ) silicon dioxide liner, are the key enablers for system integration

using silicon interposers.

Figure 5: Schematic of a 2.5D system using silicon interposer technology with key components shown [24, 25, 29].

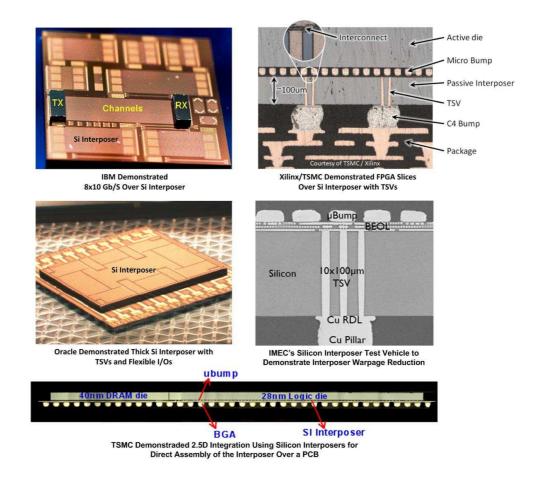

Figure 6 highlights select systems demonstrated in the literature using silicon interposers, with

- IBM's demonstration of a 21.2 mm x 21.2 mm silicon interposer consisting

of 4-level fine-pitch metallization and supporting chips with 50 μm pitch C4

microbumps to enable an 8x10 Gb/s synchronous communication between the

chips [29];

- Xilinx/TSMC's demonstration of a 25 mm x 31 mm silicon interposer (65 nm metallization) consisting of 10  $\mu$ m diameter and 100  $\mu$ m tall TSVs on a 150  $\mu$ m pitch and mounted over a second-level organic package to enable a complete 2.5D system such as an interposer supporting two 28 nm FPGA dice and two 65 nm mixed-signal dice [25, 26];

Figure 6: 2.5D system demonstrations in the literature [26–30].

- Oracle's demonstration of a 13.1 mm x 16.1 mm silicon interposer consisting of 50 μm diameter and 400 μm tall TSVs and MoCr flexible I/Os for optoelectronic Macrochip application [30];

- IMEC's demonstration of a 30 mm x 30 mm silicon interposer consisting of 10  $\mu$ m diameter and 100  $\mu$ m tall TSVs to understand and minimize warpage [28]; and

- TSMC's demonstration of a 26 mm x 24 mm silicon interposer to enable a 2.5D chip-on-wafer (CoW) technology with direct assembly of the interposer (supporting two 40 nm DRAM dice and one 28 nm logic die) over a printed circuit board (PCB) without a second-level package [27].

Despite these advances with silicon interposers, there are electrical and thermomechanical challenges with TSVs in the interposers and electrical challenges (similar to the ones for silicon ICs) with passives over the interposers. Additionally, there is a demand for optical paths for large-scale multi-interposer systems. The challenges and the needs are described as follows:

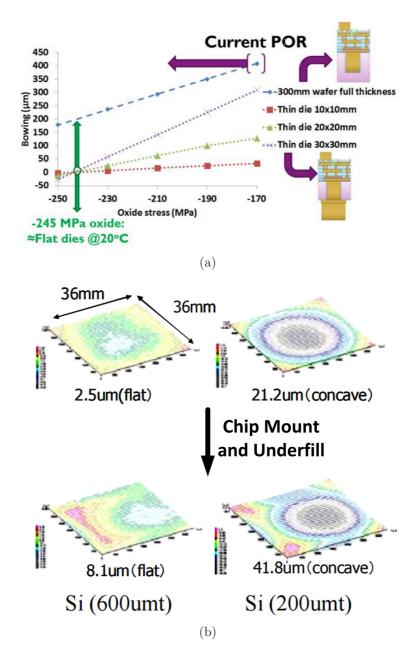

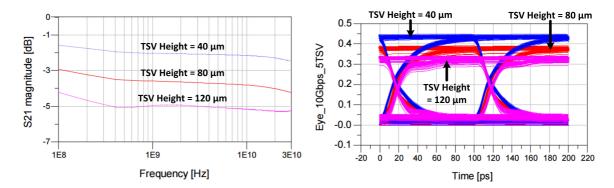

- Large-area thick interposers increase TSV loss: Large-area (limited by the reticle size) silicon interposers are desired for the integration of heterogeneous ICs with antennas and inductors close to the ICs [20,34]. Greater silicon thickness (greater than 300-400 μm) is desired for the large-area interposers to minimize warpage and bow, and improve mechanical stability as described in the following two examples: (1) Figure 7(a) demonstrates the analysis results for bow after the TSV, BEOL and bump fabrication showing a higher bow for large-area interposer dice [28]; and (2) Figure 7(b) demonstrates the warpage measurements of a 36 mm x 36 mm interposer showing reduced warpage for a thicker interposer [35]. However, increasing the interposer thickness results in longer TSVs with increased losses [36], as shown in Figure 8. These factors drive the need for low-loss TSV technologies for large-area thick interposers to compensate for the increased length.

- Silicon affects the antenna and inductor performance: The availability of a large area with silicon interposers could be leveraged to form antenna arrays for compact RF systems [20]. Moreover, it could be leveraged to form high-Q (>50) inductors close to ICs with minimized interconnect parasitics and thereby improve the performance of circuits such as digital controlled oscillators, low-noise amplifiers and power amplifiers [37]. However, the presence of a silicon interposer underneath antennas and inductors results in lower radiation efficiency and Q-factor, respectively, similar to the silicon ICs as described in

Figure 7: (a) Bow simulation for thinned interposer dice and wafer after TSV, BEOL and bump fabrication, [28] and (b) warpage measurement of silicon interposers from the BGA pad side after chip mount and underfill [35].

Section 1.1.2. This performance degradation due to silicon demands for innovative antenna and inductor integration technologies with silicon interposers.

• Issues with high-resistivity silicon and glass: High-resistivity silicon and glass interposers have been explored in the literature to address the challenges

Figure 8: Impact of TSV length on insertion loss and eye diagram [36].

with silicon [20,34]. However, high-resistivity silicon is relatively expensive and the fabrication of vias in glass is challenging. As a result, innovative interposer technologies are desired.

- CTE mismatch causes TSV stress: The coefficient of thermal expansion (CTE) mismatch between the copper and silicon results in high TSV stresses, leading to thermomechanical reliability issues such as cohesive cracks in silicon and interfacial delaminations [38]. Consequently, TSV stress reduction techniques are needed.

- Demand for the integration of optical paths: For longer interconnect distances that traverse the motherboard (between chips on different silicon interposers, for example), optical interconnects may provide a path for higher bandwidth and lower energy communication relative to conventional electrical interconnects [39]. As such, there is a need to integrate optical links with conventional electrical interconnects, including at the silicon interposer level [40].

# 1.2 Research Objective and Contribution

The objective of this research is to fabricate and characterize novel electrical TSVs that exhibit low electrical loss for silicon interposer applications and utilize the technology developed for fabricating the novel TSVs to attain high-Q inductors and high radiation efficiency antennas. To achieve the research objective, the contribution of this research includes the fabrication and characterization of photodefined polymerenhanced TSVs, and polymer-enhanced inductors and antennas obtained using the TSV photodefinition technique (Figure 9). The developed photodefined polymerenhanced technologies are described as follows:

Figure 9: Envisioned silicon interposer based system featuring photodefined (a) polymer-clad TSVs and optical TSVs that can be fabricated simultaneously, (b) polymer-embedded vias, (c) polymer-enhanced coaxial vias, and (d) polymer-enhanced inductors and antennas.

1. Photodefined polymer-clad TSVs: The proposed TSVs consist of a thicker polymer liner compared to the state-of-the-art TSVs with a thin ( $<1 \mu m$ ) silicon dioxide liner. Due to the thicker polymer liner, a reduction in TSV thermomechanical

stress, TSV dielectric capacitance and high-frequency loss is expected. An additional feature of the proposed TSVs is that they enable simultaneous fabrication of polymer-filled optical TSVs with no additional lithography steps. The optical TSVs help achieve a high-bandwidth interposer-to-interposer communication. Resistance measurements are performed for the fabricated polymer-clad TSVs and optical loss measurements are performed for the fabricated optical TSVs. To characterize strains in the fabricated polymer-clad TSVs and compare them to the TSVs with silicon dioxide liner, synchrotron x-ray diffraction (XRD) measurements are demonstrated.

- 2. Photodefined polymer-embedded vias: To attain even further reduction in TSV high-frequency loss compared to the polymer-clad TSVs, this research demonstrates the fabrication and characterization of polymer-embedded vias with copper vias embedded within polymer-filled wells in a 10  $\Omega$ -cm resistivity silicon. Since a polymer separates the copper vias, a reduction in TSV loss is expected for the fabricated polymer-embedded vias. High-frequency measurements from 100 MHz to 50 GHz and from 110 GHz to 170 GHz, and time-domain measurements up to 10 Gbps are demonstrated for the fabricated polymer-embedded vias.

- 3. Photodefined polymer-enhanced coaxial vias: To attain greater control over TSV impedance, reduce loss, and lower coupling, coaxial configuration of the polymer-embedded vias is demonstrated. High-frequency measurements up to 50 GHz are demonstrated for the fabricated coaxial vias.

- 4. Photodefined polymer-enhanced antennas and inductors: To attain higher radiation efficiency and Q-factors, polymer-enhanced antennas and inductors are demonstrated, respectively, over polymer wells. The antennas integrated over polymer wells can be utilized in the future to form antenna arrays on silicon interposers yielding compact RF systems [20]. Moreover, the proposed high-Q inductors could be utilized in the future to improve the figure of merit of digital controlled oscillators, to improve the noise figure of low-noise amplifiers, and increase the power

efficiency of power amplifiers [37].

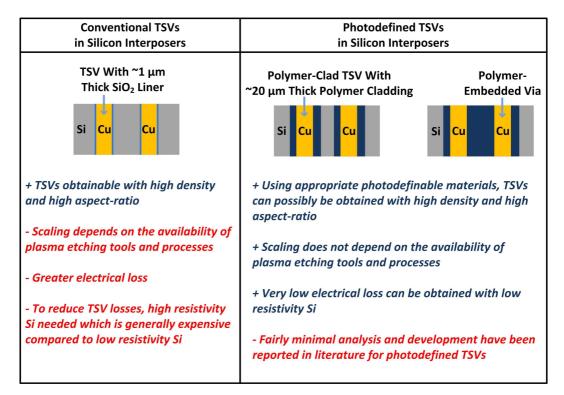

Rationale underlying photodefinition: The fabrication of the proposed TSVs in this research differs from the fabrication of the TSVs with silicon dioxide liner principally due to the fact that the fabrication of the proposed TSVs leverages the advantage of high aspect-ratio dielectric photodefinition [41], as described in Figure 10. In the fabrication of the TSVs with silicon dioxide liner, the diameter and aspect-ratio scaling depend on the availability of plasma etching tools and processes. Whereas, for the proposed TSVs obtained using dielectric photodefinition, etching requirements are relaxed since a larger area (via or trench) can easily be etched in silicon followed by polymer filling, photodefinition and electroplating. There is fairly minimal analysis and technological development reported in the literature for photodefined TSVs; S. W. Ho et al. [42] have shown the fabrication of coaxial TSVs using photodefinition to obtain impedance matching.

Figure 10: Comparison between conventional and photodefined TSVs for silicon interposers.

Hence, the rationale underlying this research is to both investigate and advance the fabrication process of photodefined TSVs that provide lower loss compared to the TSVs with silicon dioxide liner. Moreover, inductors and antennas are demonstrated in this research leveraging the expertise developed for the photodefined TSVs.

# 1.3 Organization

The dissertation is organized as follows:

- Chapter 2: The fabrication and characterization of polymer-clad TSVs with a thick polymer liner is demonstrated. Moreover, the fabrication and characterization of optical TSVs that can be obtained in parallel with the polymer-clad TSVs is also demonstrated.

- Chapter 3: The fabrication of polymer-embedded vias is demonstrated along with the challenges addressed during their fabrication.

- Chapter 4: RF and time-domain characterizations of polymer-embedded vias are demonstrated.

- Chapter 5: The fabrication and characterization of polymer-enhanced coaxial vias, antennas and inductors are demonstrated.

- Chapter 6: A summary is given and potential future work on the demonstrated technologies is described.

### CHAPTER II

# POLYMER-CLAD AND OPTICAL TSVS: FABRICATION AND CHARACTERIZATION

This chapter describes the fabrication of TSVs with thick polymer liners and optical TSVs, strain and DC characterizations of the TSVs with thick polymer liners, and optical loss characterization of the optical TSVs.

# 2.1 Literature Survey and Analysis

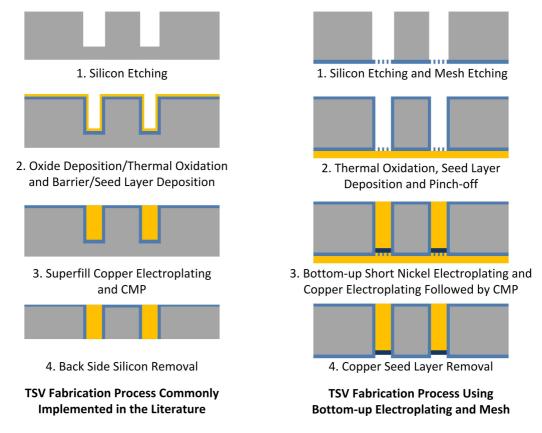

#### 2.1.1 Electrical TSV Fabrication Processes

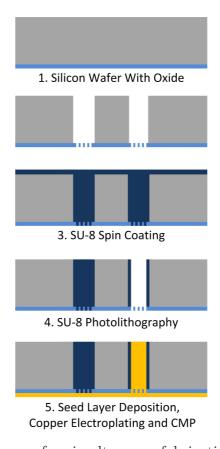

As shown in Figure 11, the fabrication process commonly used for TSVs begins with the etching of blind vias in a silicon wafer using the anisotropic BOSCH process etching followed by the formation of a dielectric liner [43, 44]. Once the dielectric liner is formed, barrier and seed layers are deposited followed by superfill copper electroplating. The additional copper obtained over the electroplated vias is removed using chemical-mechanical polishing (CMP). The additional silicon at the base of the fabricated copper-filled vias is then removed by either CMP or silicon etching to obtain TSVs.

However, voids may be obtained in the TSVs that are fabricated using the commonly implemented process. Moreover, this process requires back side silicon removal. In order to address these issues, an alternative fabrication process has been described in the literature [45] using bottom-up copper electroplating of TSVs with a group of microvias (called mesh) in the oxide layer at the base of the etched vias. The latter process is utilized in this research to develop novel TSV technologies.

Figure 11: TSV fabrication processes.

#### 2.1.2 Polymer Liner for TSVs

#### 2.1.2.1 Survey of Liner Materials and Polymer Liner Fabrication Processes

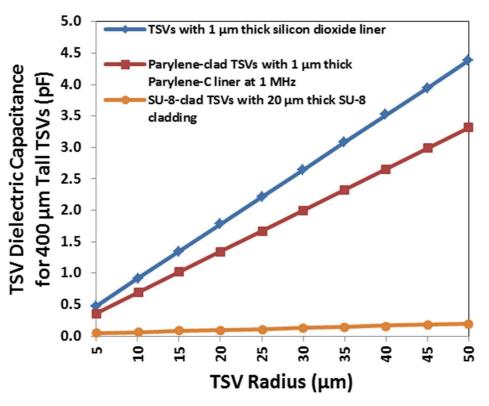

Various types of TSV liners have been described in the literature, including silicon dioxide, air and polymer. A silicon dioxide liner can either be obtained using thermal oxidation or oxide deposition. However, it is difficult to achieve conformal thick (>1  $\mu$ m) silicon dioxide liners.

Compared to the silicon dioxide liner, air liners with a lower relative dielectric constant have been described in the literature to achieve reduced TSV dielectric capacitance and loss. Thick ( $\sim 30~\mu m$ ) air liners can be fabricated by etching silicon around the fabricated TSVs [35]. Whereas, thin ( $\sim 3~\mu m$ ) air liners can be fabricated by depositing silicon dioxide over etched circular trenches in silicon until the tops of the trenches get pinched-off or alternatively by using a sacrificial material filled

in the etched circular trenches [46] followed by TSV fabrication at the center of the trenches [47].

In addition to silicon dioxide and air liners, thick polymer liners have also been described in the literature. The main advantage of using polymer liners compared to air liners is that the fabrication of horizontal interconnects is easier over thick ( $\sim$ 20  $\mu$ m) polymer liners than thick air liners.

The fabrication of polymer liners has been described in the literature using polymer vapor deposition [48], polymer filling in circular trenches within silicon [49], laser ablation of polymer-filled vias [50], and photodefinition of polymer-filled vias with a temporary release film to fabricate coaxial TSVs [42]. The photodefinition process (using SU-8 [41]) combined with the TSV fabrication process with mesh (Figure 11) is explored in this research. To better differentiate the polymer cladding fabrication processes, a comparison is shown in Table 1.

## 2.1.2.2 Survey of TSV Stress Reduction Using Polymer Liners

The thick liners fabricated using polymers with low Young's modulus can reduce TSV thermomechanical stress by acting as a cushion layer between the copper and the silicon. Various modeling results have been shown for TSVs with thick polymer liners demonstrating a reduction in TSV stresses. Using a 5  $\mu$ m thick BCB stress buffer layer for 30  $\mu$ m diameter vias, S. K. Ryu et al. [51] have shown a significant reduction in radial and shear stress along Cu/BCB and BCB/Si interfaces compared to Cu/Si interface. Using Parylene as a liner, Z. Chen et al. [52] have shown that normal stresses in copper, dielectric and silicon are lower for the TSVs with a Parylene liner compared to the TSVs with silicon dioxide liner; when the Parylene thickness is increased from 1  $\mu$ m to 15  $\mu$ m, the normal stresses in copper, dielectric and silicon are reduced by half.

Table 1: Comparison of TSV polymer cladding fabrication processes.

|   | Fabrication Method                                                 | Principle                                                                                 | Benefit                                                                                                                                                      | Limitation                                                                                                                       |

|---|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|