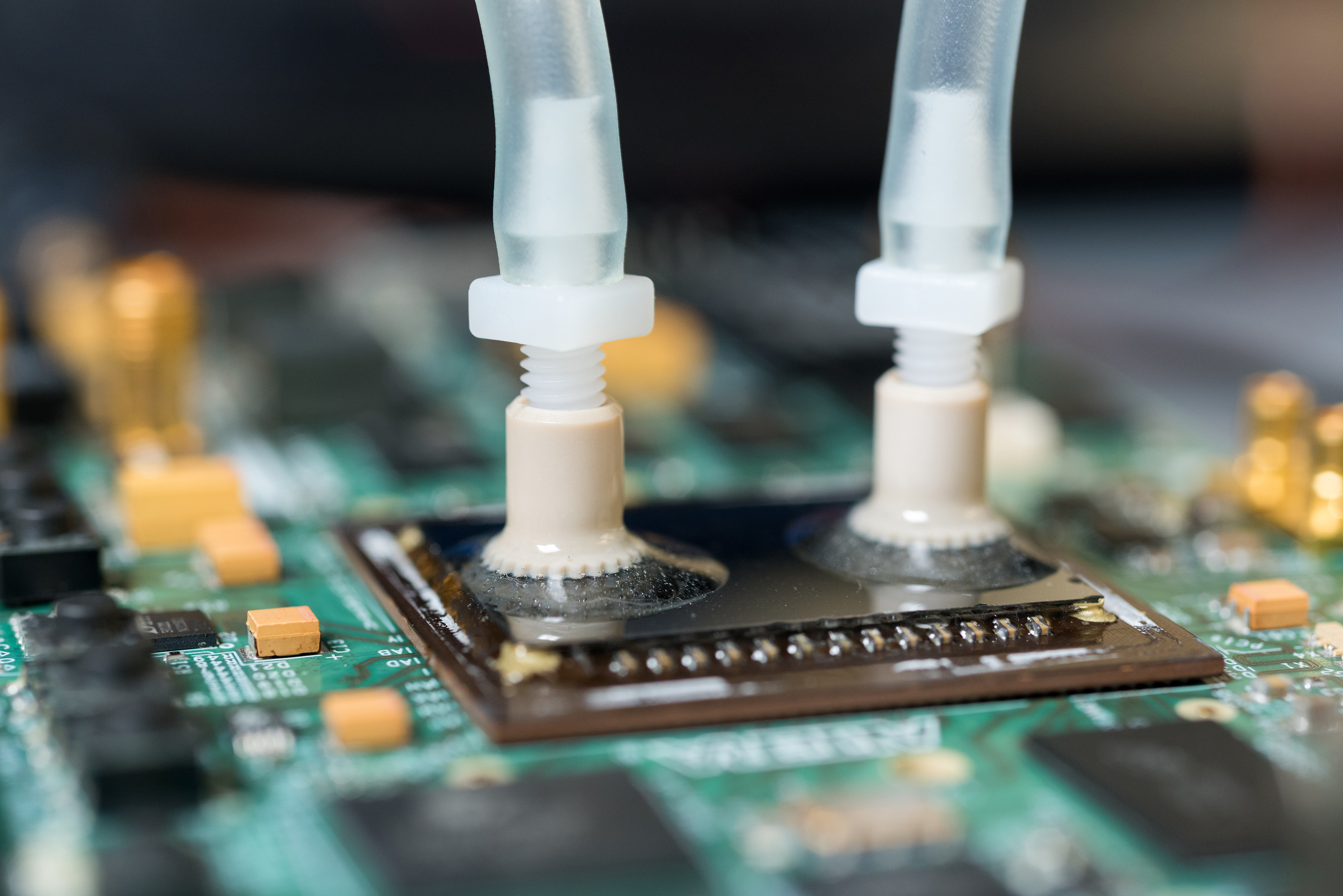

Embedded cooling in dense electronics

Interconnects have become a critical bottleneck in computing performance and efficiency at every level of integration. While the solution to this problem is decreasing interconnect length and increasing system density, the ability to remove heat already limits this approach. Computational density is primarily limited by the large volume of air that must be used to capture heat with a reasonable increase in temperature. By switching to a liquid coolant, such as water, which has a volumetric heat capacity that is more than 3000× higher than that of air (close to standard temperature and pressure), the necessary volume for heat exchange and fluid delivery can be dramatically decreased. In addition to addressing the challenge of decreasing heat sink volume, these heat sinks must be able to address the needs of modern high-power packages. These high-power accelerator packages no longer include a single monolithic die, but several dice mounted in close proximity to one another, usually with an interposer or embedded bridge chips for high-bandwidth interconnection. These dice implement heterogeneous functionalities and may exhibit significant thermal coupling through their shared heat spreader. As microelectronics transition from monolithic dice to large packages of heterogeneous chiplets, heat sinks can also be modified to match these heterogeneous designs. Monolithic and heterogeneous integration of advanced cooling technologies for 2.5D and 3D ICs represent the focus of this thrust.