Heterogeneous Integration (2.5D and 3D)

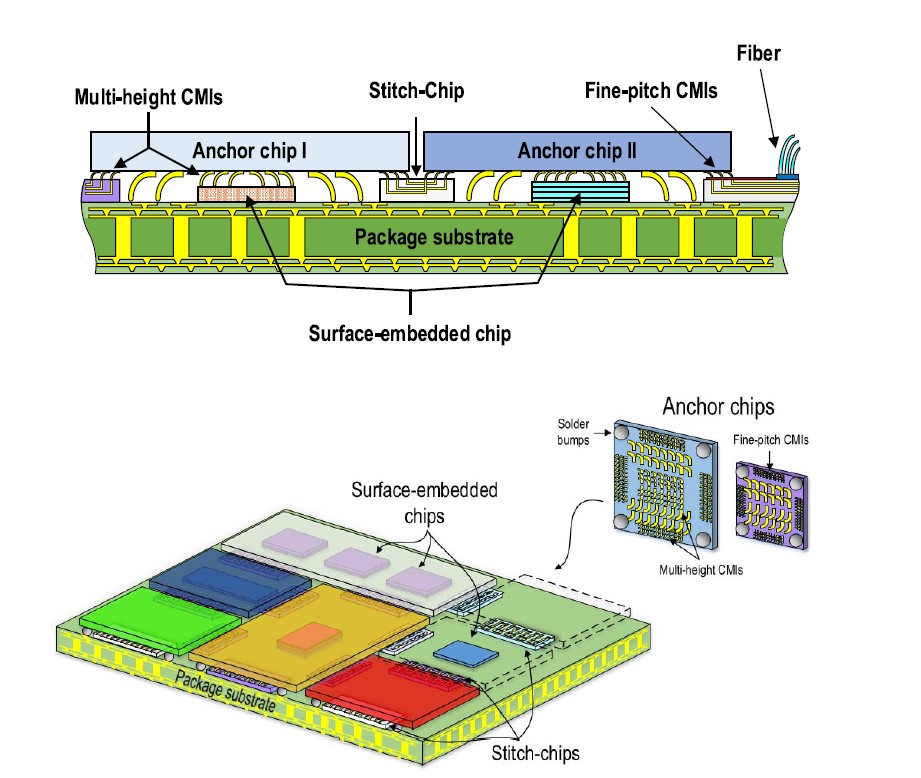

There is an ever increasing need to integrate multiple dice of various functionalities, including ASICs, CPUs, GPUs, FPGAs, microsensors, photonics, MEMS, and RF components into a single package. This need has spurred significant (perhaps exponential) research in heterogeneous interconnection platforms including 2.5D and 3D. In this thrust, we develop heterogeneous integration architectures that enable the interconnection of multiple dice (or “chiplets”) of various functionalities in a manner that mimics or exceeds monolithic-like performance, yet utilizes advanced off-chip interconnects and packaging to provide flexibility in IC fabrication and design, improved scalability, reduced development time, and reduced cost. Due to yield, cost, time to market, power dissipation, and performance considerations, 2.5D and 3D heterogeneous integration of chiplets represent a new phase for Moore’s Law. The goal of our research in this thrust is to develop radical new 2.5D and 3D heterogeneous integration architectures for electronics, photonics, and mm-wave technologies.